Difference between revisions of "फ्रीस्केल 683XX"

| Line 8: | Line 8: | ||

माइक्रोकंट्रोलर के मॉड्यूल स्वतंत्र रूप से डिज़ाइन किए गए थे और नए सीपीयू का परीक्षण किए जाने पर प्रारंभ किए गए थे। इस प्रक्रिया ने आर्किटेक्ट्स को डिज़ाइन-फॉरवर्ड करने की अनुमति दी जिससे जब सिलिकॉन प्रौद्योगिकियाँ उपलब्ध हों, तो मोटोरोला के पास कार्यान्वयन और मार्किट में जाने के लिए डिज़ाइन तैयार हों। इनमें से कई सबमॉड्यूल को प्रोसेसर की कोल्डफ़ायर लाइन में आगे ले जाया गया है। | माइक्रोकंट्रोलर के मॉड्यूल स्वतंत्र रूप से डिज़ाइन किए गए थे और नए सीपीयू का परीक्षण किए जाने पर प्रारंभ किए गए थे। इस प्रक्रिया ने आर्किटेक्ट्स को डिज़ाइन-फॉरवर्ड करने की अनुमति दी जिससे जब सिलिकॉन प्रौद्योगिकियाँ उपलब्ध हों, तो मोटोरोला के पास कार्यान्वयन और मार्किट में जाने के लिए डिज़ाइन तैयार हों। इनमें से कई सबमॉड्यूल को प्रोसेसर की कोल्डफ़ायर लाइन में आगे ले जाया गया है। | ||

माइक्रोकंट्रोलर में मॉड्यूल की | माइक्रोकंट्रोलर में मॉड्यूल की सीरीज होती है, जो इंटरनल बस से जुड़ी होती है: | ||

*डायनेमिक लॉजिक (डिजिटल लॉजिक) स्टेटिक के प्रति डायनेमिक लॉजिक सीपीयू कोर, डेड स्टॉप से अधिकतम रेटेड गति (25 या 33 मेगाहर्ट्ज) तक किसी भी क्लॉक स्पीड पर चलने में सक्षम है। | *डायनेमिक लॉजिक (डिजिटल लॉजिक) स्टेटिक के प्रति डायनेमिक लॉजिक सीपीयू कोर, डेड स्टॉप से अधिकतम रेटेड गति (25 या 33 मेगाहर्ट्ज) तक किसी भी क्लॉक स्पीड पर चलने में सक्षम है। | ||

*सीपीयू कोर जिसे परफॉरमेंस को अधिकतम करते हुए ट्रांजिस्टर को न्यूनतम करने के लिए डिज़ाइन किया गया है। | *सीपीयू कोर जिसे परफॉरमेंस को अधिकतम करते हुए ट्रांजिस्टर को न्यूनतम करने के लिए डिज़ाइन किया गया है। | ||

*डिबगिंग के लिए हाई-स्पीड क्लॉक्ड सीरियल इंटरफ़ेस जिसे [[इन-सर्किट एमुलेटर]] (बीडीएम) कहा जाता है। 683xx- | *डिबगिंग के लिए हाई-स्पीड क्लॉक्ड सीरियल इंटरफ़ेस जिसे [[इन-सर्किट एमुलेटर]] (बीडीएम) कहा जाता है। 683xx-सीरीज डिबगिंग करने के लिए सीपीयू में क्लॉक्ड सीरियल इंटरफ़ेस रखने वाली प्रथम सीरीज थी। अब, कई सीपीयू इस उद्देश्य के लिए मानक सीरियल टेस्ट इंटरफ़ेस, सामान्यतः [[JTAG|जेटैग]] का उपयोग करते हैं। | ||

*सिम (सिस्टम इंटीग्रेशन मॉड्यूल), जो चिप चयन और एड्रेस डिकोडिंग प्रदान करके अधिक प्लेन [[गोंद तर्क|ग्लू लॉजिक]] को समाप्त करता है। सिम क्लॉक जनरेटर, विभिन्न सिस्टम ऑपरेशन के लिए वॉचडॉग, प्रोसेसर पिन का कॉन्फ़िगरेशन, पीरियाडिक टाइमर और इंटरप्ट कंट्रोलर भी प्रदान करता है। | *सिम (सिस्टम इंटीग्रेशन मॉड्यूल), जो चिप चयन और एड्रेस डिकोडिंग प्रदान करके अधिक प्लेन [[गोंद तर्क|ग्लू लॉजिक]] को समाप्त करता है। सिम क्लॉक जनरेटर, विभिन्न सिस्टम ऑपरेशन के लिए वॉचडॉग, प्रोसेसर पिन का कॉन्फ़िगरेशन, पीरियाडिक टाइमर और इंटरप्ट कंट्रोलर भी प्रदान करता है। | ||

| Line 17: | Line 17: | ||

*टाइमिंग प्रोसेसर यूनिट (टीपीयू), जो लगभग किसी भी समय से संबंधित कार्य करता है: टाइमर, काउंटर, आनुपातिक पल्स विड्थ कण्ट्रोल, पल्स विड्थ मेज़रमेंट, पल्स जेनरेशन, स्टेपर मोटर कण्ट्रोल, क्वाडरेचर डिटेक्शन इत्यादि। फ्रीस्केल डेवलपमेंट सिस्टम और सोर्स कोड देता है। | *टाइमिंग प्रोसेसर यूनिट (टीपीयू), जो लगभग किसी भी समय से संबंधित कार्य करता है: टाइमर, काउंटर, आनुपातिक पल्स विड्थ कण्ट्रोल, पल्स विड्थ मेज़रमेंट, पल्स जेनरेशन, स्टेपर मोटर कण्ट्रोल, क्वाडरेचर डिटेक्शन इत्यादि। फ्रीस्केल डेवलपमेंट सिस्टम और सोर्स कोड देता है। | ||

*सहायक [[ रैंडम एक्सेस मेमोरी |रैंडम एक्सेस मेमोरी]] (रैम) टीपीयू के लिए प्रोग्रामेबल माइक्रोकंट्रोलर स्टोर के रूप में कार्य करती है। | *सहायक [[ रैंडम एक्सेस मेमोरी |रैंडम एक्सेस मेमोरी]] (रैम) टीपीयू के लिए प्रोग्रामेबल माइक्रोकंट्रोलर स्टोर के रूप में कार्य करती है। | ||

*कुछ प्रारंभिक मॉडलों में दो | *कुछ प्रारंभिक मॉडलों में दो कन्वेंशनल काउंटर-टाइमर होते हैं। | ||

*जनरल पर्पस टाइमर (जीपीटी) मॉड्यूल पल्स | *जनरल पर्पस टाइमर (जीपीटी) मॉड्यूल पल्स एक्कूमूलेटर्स, कैप्चर/कम्पेयर और [[पल्स चौड़ाई उतार - चढ़ाव|पल्स विड्थ मॉडुलेशन]] क्षमताएं प्रदान करता है। | ||

*कुछ मॉडलों में [[संचार प्रोसेसर मॉड्यूल|नेटवर्क प्रोसेसर मॉड्यूल]] (सीपीएम) और सीरियल प्रोसेसर मोडूल (एससीसी) के रूप में [[ नेटवर्क इंटरफ़ेस प्रोसेसर |नेटवर्क इंटरफ़ेस प्रोसेसर]] होता है जिसे [[ईथरनेट]] या [[एचडीएलसी]] बसों से इंटरफेस किया जा सकता है। | *कुछ मॉडलों में [[संचार प्रोसेसर मॉड्यूल|नेटवर्क प्रोसेसर मॉड्यूल]] (सीपीएम) और सीरियल प्रोसेसर मोडूल (एससीसी) के रूप में [[ नेटवर्क इंटरफ़ेस प्रोसेसर |नेटवर्क इंटरफ़ेस प्रोसेसर]] होता है जिसे [[ईथरनेट]] या [[एचडीएलसी]] बसों से इंटरफेस किया जा सकता है। | ||

*अधिकांश मॉडलों में केओइड सीरियल मॉड्यूल (क्यूएसएम) होता है जो सिंक्रोनस [[ क्रमानुसार बाह्य इंटरफ़ेस |सीरियल पेरिफेरल इंटरफ़ेस]] (एसपीआई) और लॉजिक-लेवल आरएस-232 [[यूएआरटी]] क्षमताएं दोनों प्रदान करता है। | *अधिकांश मॉडलों में केओइड सीरियल मॉड्यूल (क्यूएसएम) होता है जो सिंक्रोनस [[ क्रमानुसार बाह्य इंटरफ़ेस |सीरियल पेरिफेरल इंटरफ़ेस]] (एसपीआई) और लॉजिक-लेवल आरएस-232 [[यूएआरटी]] क्षमताएं दोनों प्रदान करता है। | ||

Revision as of 21:41, 12 August 2023

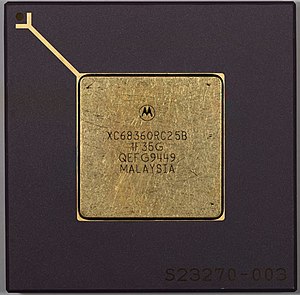

फ्रीस्केल 683xx (पूर्व में मोटोरोला 683xx) फ्रीस्केल द्वारा संगत माइक्रोकंट्रोलर की फैमिली है जो मोटोरोला 68000-आधारित सीपीयू कोर का उपयोग करता है। फैमिली को हार्डवेयर डिस्क्रिप्शन लैंग्वेज का उपयोग करके डिज़ाइन किया गया था, जिससे भागों को संश्लेषित किया जा सके, और उत्तम निर्माण प्रक्रियाओं जैसे डाई श्रिंक्स के लिए उत्तरदायी बनाया जा सके।

683xx फैमिली में दो सीपीयू कोर का उपयोग किया जाता है: मोटोरोला 68EC000 और सीपीयू32 कोर का निर्देश सेट बिटफील्ड निर्देशों के बिना मोटोरोला 68020 के समान है, और सीपीयू32 कोर के लिए अद्वितीय कुछ निर्देश हैं, जैसे टेबल लुकअप और इंटरपोलेट निर्देश, और लो-पावर स्टॉप मोड आदि।

माइक्रोकंट्रोलर के मॉड्यूल स्वतंत्र रूप से डिज़ाइन किए गए थे और नए सीपीयू का परीक्षण किए जाने पर प्रारंभ किए गए थे। इस प्रक्रिया ने आर्किटेक्ट्स को डिज़ाइन-फॉरवर्ड करने की अनुमति दी जिससे जब सिलिकॉन प्रौद्योगिकियाँ उपलब्ध हों, तो मोटोरोला के पास कार्यान्वयन और मार्किट में जाने के लिए डिज़ाइन तैयार हों। इनमें से कई सबमॉड्यूल को प्रोसेसर की कोल्डफ़ायर लाइन में आगे ले जाया गया है।

माइक्रोकंट्रोलर में मॉड्यूल की सीरीज होती है, जो इंटरनल बस से जुड़ी होती है:

- डायनेमिक लॉजिक (डिजिटल लॉजिक) स्टेटिक के प्रति डायनेमिक लॉजिक सीपीयू कोर, डेड स्टॉप से अधिकतम रेटेड गति (25 या 33 मेगाहर्ट्ज) तक किसी भी क्लॉक स्पीड पर चलने में सक्षम है।

- सीपीयू कोर जिसे परफॉरमेंस को अधिकतम करते हुए ट्रांजिस्टर को न्यूनतम करने के लिए डिज़ाइन किया गया है।

- डिबगिंग के लिए हाई-स्पीड क्लॉक्ड सीरियल इंटरफ़ेस जिसे इन-सर्किट एमुलेटर (बीडीएम) कहा जाता है। 683xx-सीरीज डिबगिंग करने के लिए सीपीयू में क्लॉक्ड सीरियल इंटरफ़ेस रखने वाली प्रथम सीरीज थी। अब, कई सीपीयू इस उद्देश्य के लिए मानक सीरियल टेस्ट इंटरफ़ेस, सामान्यतः जेटैग का उपयोग करते हैं।

- सिम (सिस्टम इंटीग्रेशन मॉड्यूल), जो चिप चयन और एड्रेस डिकोडिंग प्रदान करके अधिक प्लेन ग्लू लॉजिक को समाप्त करता है। सिम क्लॉक जनरेटर, विभिन्न सिस्टम ऑपरेशन के लिए वॉचडॉग, प्रोसेसर पिन का कॉन्फ़िगरेशन, पीरियाडिक टाइमर और इंटरप्ट कंट्रोलर भी प्रदान करता है।

683xx फैमिली में विभिन्न प्रोसेसर पर उपलब्ध अन्य मॉड्यूल हैं:

- टाइमिंग प्रोसेसर यूनिट (टीपीयू), जो लगभग किसी भी समय से संबंधित कार्य करता है: टाइमर, काउंटर, आनुपातिक पल्स विड्थ कण्ट्रोल, पल्स विड्थ मेज़रमेंट, पल्स जेनरेशन, स्टेपर मोटर कण्ट्रोल, क्वाडरेचर डिटेक्शन इत्यादि। फ्रीस्केल डेवलपमेंट सिस्टम और सोर्स कोड देता है।

- सहायक रैंडम एक्सेस मेमोरी (रैम) टीपीयू के लिए प्रोग्रामेबल माइक्रोकंट्रोलर स्टोर के रूप में कार्य करती है।

- कुछ प्रारंभिक मॉडलों में दो कन्वेंशनल काउंटर-टाइमर होते हैं।

- जनरल पर्पस टाइमर (जीपीटी) मॉड्यूल पल्स एक्कूमूलेटर्स, कैप्चर/कम्पेयर और पल्स विड्थ मॉडुलेशन क्षमताएं प्रदान करता है।

- कुछ मॉडलों में नेटवर्क प्रोसेसर मॉड्यूल (सीपीएम) और सीरियल प्रोसेसर मोडूल (एससीसी) के रूप में नेटवर्क इंटरफ़ेस प्रोसेसर होता है जिसे ईथरनेट या एचडीएलसी बसों से इंटरफेस किया जा सकता है।

- अधिकांश मॉडलों में केओइड सीरियल मॉड्यूल (क्यूएसएम) होता है जो सिंक्रोनस सीरियल पेरिफेरल इंटरफ़ेस (एसपीआई) और लॉजिक-लेवल आरएस-232 यूएआरटी क्षमताएं दोनों प्रदान करता है।

यह भी देखें

- क्यूयूआईसीसी (क्वाड इंटीग्रेटेड कम्युनिकेशंस कंट्रोलर)

बाहरी संबंध

- Collapse templates

- Navigational boxes

- Navigational boxes without horizontal lists

- Sidebars with styles needing conversion

- Templates generating microformats

- Templates that are not mobile friendly

- Wikipedia metatemplates

- फ्रीस्केल सेमीकंडक्टर माइक्रोकंट्रोलर

- मोटोरोला माइक्रोकंट्रोलर

- 68k माइक्रोप्रोसेसर

- Machine Translated Page

- Created On 09/08/2023