डोमेन-विशिष्ट वास्तुकला

एक डोमेन-विशिष्ट आर्किटेक्चर (डीएसए) एक प्रोग्राम योग्य कंप्यूटर आर्किटेक्चर है जिसे विशेष रूप से किसी दिए गए एप्लिकेशन डोमेन की सीमा के भीतर बहुत कुशलता से संचालित करने के लिए तैयार किया गया है। इस शब्द का प्रयोग अक्सर CPU जैसे सामान्य प्रयोजन आर्किटेक्चर के विपरीत किया जाता है, जो किसी भी कंप्यूटर प्रोग्राम पर काम करने के लिए डिज़ाइन किया गया है।[1]

इतिहास

1960 के दशक में शुरू हुए अर्धचालक उपकरण बूम के संयोजन में, कंप्यूटर आर्किटेक्ट्स को बड़ी संख्या में उपलब्ध ट्रांजिस्टर का फायदा उठाने के नए तरीके खोजने का काम सौंपा गया था। मूर का नियम|मूर का नियम और डेनार्ड स्केलिंग ने आर्किटेक्ट्स को सामान्य प्रयोजन कार्यक्रमों पर सामान्य प्रयोजन माइक्रोप्रोसेसर के प्रदर्शन को बेहतर बनाने पर ध्यान केंद्रित करने में सक्षम बनाया।[2][3] इन प्रयासों से कई तकनीकी नवाचार सामने आए, जैसे [[बहुस्तरीय कैश]]|मल्टी-लेवल कैश, आउट-ऑफ-ऑर्डर निष्पादन, डीप इंस्ट्रक्शन निर्देश पाइपलाइन , मल्टीथ्रेडिंग (कंप्यूटर आर्किटेक्चर), और मल्टीप्रोसेसिंग। इन नवाचारों का प्रभाव कल्पना जैसे गणना में सामान्यवादी बेंचमार्क पर मापा गया था, और आर्किटेक्ट इन कार्यक्रमों की आंतरिक संरचना या विशिष्ट विशेषताओं से चिंतित नहीं थे।[1] डेनार्ड स्केलिंग के अंत ने कंप्यूटर आर्किटेक्ट्स को एक एकल, बहुत तेज़ प्रोसेसर से कई मल्टी-कोर प्रोसेसर पर स्विच करने के लिए प्रेरित किया। प्रदर्शन में सुधार अब केवल एक कोर की ऑपरेटिंग आवृत्ति को बढ़ाकर हासिल नहीं किया जा सकता है।[4] मूर के नियम के अंत ने ध्यान को सामान्य प्रयोजन आर्किटेक्चर से हटाकर अधिक विशिष्ट हार्डवेयर की ओर स्थानांतरित कर दिया। यद्यपि सामान्य-उद्देश्य सीपीयू की किसी भी कंप्यूटर प्रणाली में जगह होने की संभावना है, सामान्य-उद्देश्य और डोमेन-विशिष्ट घटकों से बना विषम प्रणाली वास्तुकला उच्च प्रदर्शन प्राप्त करने के लिए सबसे हालिया प्रवृत्ति है।[citation needed]

जबकि सेमीकंडक्टर उद्योग की स्थापना के बाद से हार्डवेयर त्वरण और एप्लिकेशन-विशिष्ट एकीकृत सर्किट का उपयोग बहुत विशिष्ट एप्लिकेशन डोमेन में किया गया है, वे आम तौर पर बहुत सीमित लचीलेपन के साथ एक विशिष्ट फ़ंक्शन को कार्यान्वित करते हैं। इसके विपरीत, डोमेन-विशिष्ट आर्किटेक्चर की ओर बदलाव लचीलेपन और विशेषज्ञता का बेहतर संतुलन हासिल करना चाहता है।[5] डोमेन-विशिष्ट प्रोग्रामयोग्य आर्किटेक्चर का एक उल्लेखनीय प्रारंभिक उदाहरण ग्राफ़िक्स प्रोसेसिंग यूनिट|जीपीयू हैं। ये विशेष हार्डवेयर विशेष रूप से डिजिटल इमेज प्रोसेसिंग और कंप्यूटर चित्रलेख के क्षेत्र में संचालित करने के लिए विकसित किए गए थे।[6] इन प्रोग्रामयोग्य प्रसंस्करण इकाइयों को विडियो गेम कंसोल और पर्सनल कंप्यूटर दोनों में व्यापक रूप से अपनाया गया। NVIDIA और एएमडी जीपीयू दोनों के लिए हार्डवेयर/सॉफ्टवेयर स्टैक के सुधार के साथ, छवि प्रसंस्करण के क्षेत्र के बाहर भी, बड़े पैमाने पर समानांतर और शर्मनाक समानांतर कार्यों के त्वरण के लिए इन आर्किटेक्चर का अधिक से अधिक उपयोग किया जा रहा है।[7] 2010 के दशक में यंत्र अधिगम |मशीन-लर्निंग-आधारित कृत्रिम बुद्धिमत्ता के पुनर्जागरण के बाद से, कृत्रिम तंत्रिका नेटवर्क के विभिन्न रूपों के अनुमान में तेजी लाने के लिए कई डोमेन-विशिष्ट आर्किटेक्चर विकसित किए गए हैं। कुछ उदाहरण हैं Google|Google की Tensor प्रोसेसिंग यूनिट, NVIDIA की NVDLA[8] और आर्म (कंपनी) की एमएलपी।[9]

डीएसए डिज़ाइन के लिए दिशानिर्देश

जॉन एल. हेनेसी और डेविड पैटरसन (कंप्यूटर वैज्ञानिक) ने डीएसए डिजाइन के लिए पांच सिद्धांतों की रूपरेखा तैयार की, जिससे बेहतर क्षेत्र दक्षता और ऊर्जा बचत होती है। इस प्रकार की वास्तुकला में उद्देश्य अक्सर गैर-आवर्ती इंजीनियरिंग (एनआरई) लागत को कम करना भी होता है ताकि किसी विशेष समाधान में निवेश को अधिक आसानी से परिशोधित किया जा सके।[1]

- डेटा को स्थानांतरित करने की दूरी को कम करें: सामान्य प्रयोजन मेमोरी पदानुक्रम में डेटा को स्थानांतरित करने के लिए डेटा तक पहुंचने में विलंब को कम करने का प्रयास करने के लिए उल्लेखनीय मात्रा में ऊर्जा की आवश्यकता होती है। डोमेन-विशिष्ट आर्किटेक्चर के मामले में, यह उम्मीद की जाती है कि हार्डवेयर और संकलक डिजाइनरों द्वारा एप्लिकेशन डोमेन को समझने से सरल और विशेष मेमोरी पदानुक्रम की अनुमति मिलती है, जहां डेटा मूवमेंट को बड़े पैमाने पर सॉफ्टवेयर में नियंत्रित किया जाता है, जिसमें विशिष्ट कार्यों के लिए दर्जी की गई यादें होती हैं। कार्यक्षेत्र।[1]# सहेजे गए संसाधनों को अंकगणितीय इकाइयों या बड़ी यादों में निवेश करें: चूंकि आउट-ऑफ़-ऑर्डर निष्पादन, प्रीफ़ेचिंग (कंप्यूटिंग), एड्रेस कोलेसिंग (कंप्यूटर विज्ञान), और जैसे सामान्य प्रयोजन वास्तुशिल्प अनुकूलन को छोड़कर हार्डवेयर संसाधनों की एक उल्लेखनीय मात्रा को बचाया जा सकता है। हार्डवेयर अटकलें, सहेजे गए संसाधनों को उपलब्ध समानता (कंप्यूटिंग) का अधिकतम दोहन करने के लिए फिर से निवेश किया जाना चाहिए, उदाहरण के लिए, अधिक अंकगणितीय इकाइयां जोड़कर या बड़ी यादें जोड़कर किसी भी मेमोरी बैंडविड्थ समस्या को हल करना।[1]# डोमेन से मेल खाने वाले समानता के सबसे आसान रूप का उपयोग करें: चूंकि लक्ष्य एप्लिकेशन डोमेन लगभग हमेशा समानता का एक अंतर्निहित रूप प्रस्तुत करते हैं, इसलिए यह तय करना महत्वपूर्ण है कि इस समानता का लाभ कैसे उठाया जाए और इसे सॉफ़्टवेयर के सामने कैसे लाया जाए। यदि, उदाहरण के लिए, एक Simd आर्किटेक्चर डोमेन में काम कर सकता है, तो प्रोग्रामर के लिए MIMD आर्किटेक्चर की तुलना में इसका उपयोग करना आसान होगा।[1]# डोमेन के लिए आवश्यक डेटा आकार और प्रकार को सरलतम तक कम करें: जब भी संभव हो, संकीर्ण और सरल डेटा प्रकार का उपयोग करने से कई फायदे मिलते हैं। उदाहरण के लिए, यह मेमोरी-बाउंड फ़ंक्शन|मेमोरी-बाउंड अनुप्रयोगों के लिए डेटा ले जाने की लागत को कम करता है, और यह संबंधित अंकगणितीय इकाइयों को लागू करने के लिए आवश्यक संसाधनों की मात्रा को भी कम कर सकता है।[1]# डीएसए में कोड पोर्ट करने के लिए एक डोमेन-विशिष्ट प्रोग्रामिंग भाषा का उपयोग करें: डीएसए के लिए चुनौतियों में से एक उपयोग में आसानी है, और अधिक विशेष रूप से, आर्किटेक्चर को प्रभावी ढंग से प्रोग्राम करने और उस पर एप्लिकेशन चलाने में सक्षम होना है। जब भी संभव हो, मौजूदा डोमेन-विशिष्ट भाषा | डोमेन-विशिष्ट भाषाएं (डीएसएल) जैसे हैलाइड (प्रोग्रामिंग भाषा) का उपयोग करने की सलाह दी जाती है।[10] और टेंसरफ़्लो [11] DSA को अधिक आसानी से प्रोग्राम करने के लिए। मौजूदा कंपाइलर टूलचेन और सॉफ्टवेयर फ्रेमवर्क का पुन: उपयोग नए डीएसए के उपयोग को काफी अधिक सुलभ बनाता है।[1]

गहरे तंत्रिका नेटवर्क के लिए डीएसए

एप्लिकेशन डोमेन में से एक जहां डीएसए को सबसे अधिक सफलता मिली है वह कृत्रिम बुद्धिमत्ता है। विशेष रूप से, डीप न्यूरल नेटवर्क (डीएनएन) के त्वरण के लिए कई आर्किटेक्चर विकसित किए गए हैं।[12] निम्नलिखित अनुभागों में, हम कुछ उदाहरणों की रिपोर्ट करते हैं।

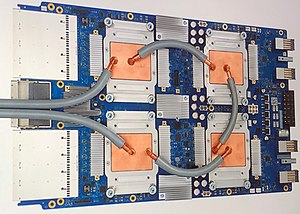

Tensor Processing Unit 3.0 | |

| Designer | |

|---|---|

| Introduced | May 2016 |

| Type | Neural network Machine learning |

टीपीयू

Google की टेंसर प्रोसेसिंग यूनिट को 2015 में DNN अनुमान में तेजी लाने के लिए विकसित किया गया था क्योंकि कंपनी ने अनुमान लगाया था कि ध्वनि खोज के उपयोग के लिए तंत्रिका नेटवर्क अनुमान के लिए उस समय आवंटित कम्प्यूटेशनल संसाधनों को दोगुना करने की आवश्यकता होगी।[13] टीपीयू को पीसीआई एक्सप्रेस बस के माध्यम से संचार करने वाले एक सह प्रोसेसर | सह-प्रोसेसर के रूप में डिज़ाइन किया गया था, जिसे मौजूदा सर्वर में आसानी से शामिल किया जा सके। यह मुख्य रूप से सीआईएससी (कॉम्प्लेक्स इंस्ट्रक्शन सेट कंप्यूटर) अनुदेश सेट वास्तुकला के बाद एक मैट्रिक्स गुणन | मैट्रिक्स-गुणन इंजन है। गुणन इंजन ऊर्जा बचाने के लिए सिस्टोलिक सरणी का उपयोग करता है, जिससे वाष्पशील मेमोरी में लिखने की संख्या कम हो जाती है।[14] टीपीयू को 28-एनएम प्रक्रिया के साथ निर्मित किया गया था और 700 मेगाहर्ट्ज पर क्लॉक किया गया था। एप्लिकेशन का वह भाग जो TPU पर चलता है, TensorFlow में कार्यान्वित किया जाता है।[14] टीपीयू मुख्य रूप से कम सटीक पूर्णांकों की गणना करता है, जो ऊर्जा बचत और बेहतर प्रदर्शन में योगदान देता है।[14]

माइक्रोसॉफ्ट कैटापल्ट

माइक्रोसॉफ्ट का प्रोजेक्ट कैटापुल्ट[15] सर्वर पर चल रहे विभिन्न अनुप्रयोगों को तेज करने के लिए एफपीजीए का उपयोग करने के विचार के साथ, कई अलग-अलग अनुप्रयोगों को तेज करने के लिए एफपीजीए की पुन: कॉन्फ़िगरेशन क्षमताओं का लाभ उठाने के विचार के साथ, पीसीआईई बस के माध्यम से डेटा सेंटर सर्वर में एक क्षेत्र में प्रोग्राम की जा सकने वाली द्वार श्रंखला को कनेक्ट करें।

Google के TPU से भिन्न, कैटापुल्ट FPGA को हार्डवेयर विवरण भाषा|हार्डवेयर-विवरण भाषाओं जैसे Verilog और VHDL के माध्यम से प्रोग्राम करने की आवश्यकता है। इस कारण से, फ्रेमवर्क के लेखकों के लिए एक बड़ी चिंता सीमित प्रोग्रामयोग्यता थी।[16] माइक्रोसॉफ्ट ने कैटापुल्ट फ्रेमवर्क के लिए एक संवादात्मक तंत्रिका नेटवर्क एक्सेलेरेटर डिज़ाइन किया था जिसे मुख्य रूप से माइक्रोसॉफ्ट बिंग सर्च इंजन में रैंकिंग फ़ंक्शन को तेज करने के लिए डिज़ाइन किया गया था। प्रस्तावित आर्किटेक्चर ने दो-आयामी सिस्टोलिक सरणी के आधार पर एक रनटाइम पुन: कॉन्फ़िगर करने योग्य डिज़ाइन प्रदान किया।[17][18]

एनवीडीएलए

NVDLA, NVIDIA का गहन-शिक्षण अनुमान त्वरक है। यह एक ओपन-सोर्स हार्डवेयर|ओपन-सोर्स हार्डवेयर डिज़ाइन है जो कई उच्च पैरामीट्रिजेबल कॉन्फ़िगरेशन में उपलब्ध है। छोटे-एनवीडीएलए मॉडल को चीजों की इंटरनेट जैसे संसाधन-बाधित परिदृश्यों में तैनात करने के लिए डिज़ाइन किया गया है जहां लागत, क्षेत्र और बिजली मुख्य चिंताएं हैं। इसके विपरीत। बड़े-एनवीडीएलए मॉडल उच्च-प्रदर्शन कंप्यूटिंग परिदृश्यों के लिए अधिक उपयुक्त है। एनवीडीएलए अपना स्वयं का समर्पित प्रशिक्षण बुनियादी ढांचा, संकलन उपकरण और रनटाइम सॉफ़्टवेयर स्टैक प्रदान करता है।[19]

अन्य डोमेन के लिए डीएसए

कृत्रिम बुद्धिमत्ता में एक अनुप्रयोग के अलावा, वैज्ञानिक कंप्यूटिंग, छवि प्रसंस्करण और नेटवर्किंग के भीतर कई डोमेन में डीएसए को अपनाया जा रहा है।[20][21]

पिक्सेल विज़ुअल कोर

पिक्सेल विज़ुअल कोर (पीवीसी) Google द्वारा डिज़ाइन किया गया ARM एआरएम वास्तुकला|ARM-आधारित छवि संसाधक है। पीवीसी मोबाइल उपकरणों और भविष्य में इंटरनेट ऑफ थिंग्स के लिए पूरी तरह से प्रोग्राम करने योग्य इमेज प्रोसेसर, दृष्टि प्रसंस्करण इकाई और ऐ त्वरक मल्टी-कोर डोमेन-विशिष्ट आर्किटेक्चर (डीएसए) है। यह पहली बार Google Pixel 2 में दिखाई दिया, जिसे 19 अक्टूबर, 2017 को पेश किया गया था। यह Google Pixel 3 में भी दिखाई दिया है। Pixel 4 से शुरू होकर, इस चिप को Pixel न्यूरल कोर से बदल दिया गया था।[22]

एंटोनियस

एंटोन3 एक डीएसए है जिसे आणविक गतिशीलता|आणविक-गतिकी सिमुलेशन की कुशलतापूर्वक गणना करने के लिए डिज़ाइन किया गया है। यह कई कंप्यूटिंग नोड्स को जोड़ने के लिए एक विशेष 3डी टोरस्र्स टोपोलॉजी इंटरकनेक्शन नेटवर्क का उपयोग करता है।[21] प्रत्येक कंप्यूटिंग नोड में मेष टोपोलॉजी के माध्यम से परस्पर जुड़े हुए 64 कोर का एक सेट होता है। अणुओं के बीच बल क्षेत्र (रसायन विज्ञान)|बल-क्षेत्र की कुशलतापूर्वक गणना करने के लिए कोर एक विशेष गहरी पाइपलाइन लागू करते हैं। यह विषम प्रणाली रिकॉर्ड-ब्रेकिंग सिमुलेशन गति प्राप्त करने के लिए सामान्य-उद्देश्यीय हार्डवेयर और डोमेन-विशिष्ट घटकों को जोड़ती है।[23]

संदर्भ

- ↑ 1.0 1.1 1.2 1.3 1.4 1.5 1.6 1.7 Hennessy, John L.; Patterson, David A. (2019). Computer architecture: a quantitative approach. Krste Asanović (6 ed.). Cambridge, Mass: Morgan Kaufmann Publishers, an imprint of Elsevier. p. 540. ISBN 978-0-12-811905-1.

- ↑ Moore, G.E. (January 1998). "एकीकृत सर्किट पर अधिक घटकों को भरना". Proceedings of the IEEE. 86 (1): 82–85. doi:10.1109/jproc.1998.658762. ISSN 0018-9219.

- ↑ Dennard, R.H.; Gaensslen, F.H.; Yu, Hwa-Nien; Rideout, V.L.; Bassous, E.; LeBlanc, A.R. (October 1974). "बहुत छोटे भौतिक आयामों के साथ आयन-प्रत्यारोपित MOSFET का डिज़ाइन". IEEE Journal of Solid-State Circuits. 9 (5): 256–268. Bibcode:1974IJSSC...9..256D. doi:10.1109/jssc.1974.1050511. ISSN 0018-9200. S2CID 283984.

- ↑ Schauer, Bryan. "Multicore Processors – A Necessity" (PDF). Archived from the original (PDF) on 2011-11-25. Retrieved 2023-07-06.

- ↑ Barr, Keith Elliott (2007). ASIC design in the silicon sandbox: a complete guide to building mixed-signal integrated circuits. New York: McGraw-Hill. ISBN 978-0-07-148161-8.

- ↑ "What is a GPU?". Virtual Desktop. Retrieved 2023-07-07.

- ↑ "NVIDIA त्वरित अनुप्रयोग". NVIDIA. Retrieved 2023-07-06.

- ↑ "एनवीडीएलए - माइक्रोआर्किटेक्चर - एनवीडिया - विकीचिप". en.wikichip.org. Retrieved 2023-07-06.

- ↑ "मशीन लर्निंग प्रोसेसर (एमएलपी) - माइक्रोआर्किटेक्चर - एआरएम - विकीचिप". en.wikichip.org. Retrieved 2023-07-06.

- ↑ Ragan-Kelley, Jonathan. "halide". halide-lang.org. Retrieved 2023-07-06.

- ↑ "टेंसरफ़्लो". टेंसरफ़्लो. Retrieved 2023-07-06.

- ↑ Ghayoumi, Mehdi (2021-10-12), "Deep Neural Networks (DNNs) Fundamentals and Architectures", Deep Learning in Practice, Boca Raton: Chapman and Hall/CRC, pp. 77–107, doi:10.1201/9781003025818-5, ISBN 9781003025818, S2CID 241427658, retrieved 2023-07-06

- ↑ Hennessy, John L.; Patterson, David A. (2019). Computer architecture: a quantitative approach. Krste Asanović (6 ed.). Cambridge, Mass: Morgan Kaufmann Publishers, an imprint of Elsevier. p. 557. ISBN 978-0-12-811905-1.

- ↑ 14.0 14.1 14.2 Hennessy, John L.; Patterson, David A. (2019). Computer architecture: a quantitative approach. Krste Asanović (6 ed.). Cambridge, Mass: Morgan Kaufmann Publishers, an imprint of Elsevier. p. 560. ISBN 978-0-12-811905-1.

- ↑ "प्रोजेक्ट कैटापल्ट". Microsoft Research. Retrieved 2023-07-06.

- ↑ Putnam, Andrew; Caulfield, Adrian M.; Chung, Eric S.; Chiou, Derek; Constantinides, Kypros; Demme, John; Esmaeilzadeh, Hadi; Fowers, Jeremy; Gopal, Gopi Prashanth; Gray, Jan; Haselman, Michael; Hauck, Scott; Heil, Stephen; Hormati, Amir; Kim, Joo-Young (2016-10-28). "बड़े पैमाने पर डेटासेंटर सेवाओं में तेजी लाने के लिए एक पुन: कॉन्फ़िगर करने योग्य फैब्रिक". Communications of the ACM. 59 (11): 114–122. doi:10.1145/2996868. ISSN 0001-0782. S2CID 3826382.

- ↑ Hennessy, John L.; Patterson, David A. (2019). Computer architecture: a quantitative approach. Krste Asanović (6 ed.). Cambridge, Mass: Morgan Kaufmann Publishers, an imprint of Elsevier. p. 573. ISBN 978-0-12-811905-1.

- ↑ "पेंगुइन के बीच एक चुम्बन". Bing. Retrieved 2023-07-06.

- ↑ "NVDLA Primer — NVDLA Documentation". nvdla.org. Retrieved 2023-07-06.

- ↑ "NVIDIA ब्लूफ़ील्ड डेटा प्रोसेसिंग यूनिट (DPU)". NVIDIA. Retrieved 2023-07-06.

- ↑ 21.0 21.1 Shaw, David E.; Adams, Peter J.; Azaria, Asaph; Bank, Joseph A.; Batson, Brannon; Bell, Alistair; Bergdorf, Michael; Bhatt, Jhanvi; Butts, J. Adam; Correia, Timothy; Dirks, Robert M.; Dror, Ron O.; Eastwood, Michael P.; Edwards, Bruce; Even, Amos (2021-11-14). "Anton 3: Twenty microseconds of molecular dynamics simulation before lunch". उच्च प्रदर्शन कंप्यूटिंग, नेटवर्किंग, भंडारण और विश्लेषण के लिए अंतर्राष्ट्रीय सम्मेलन की कार्यवाही. ACM. pp. 1–11. doi:10.1145/3458817.3487397. ISBN 978-1-4503-8442-1. S2CID 239036976.

- ↑ Cutress, Ian. "Hot Chips 2018: The Google Pixel Visual Core Live Blog (10am PT, 5pm UTC)". www.anandtech.com. Retrieved 2023-07-07.

- ↑ Russell, John (2021-09-02). "Anton 3 Is a 'Fire-Breathing' Molecular Simulation Beast". HPCwire. Retrieved 2023-07-06.

अग्रिम पठन

- Computer Architecture. A Quantitative Approach. Sixth Edition. John L. Hennessy. Stanford University. David A. Patterson. University of California, Berkeley.

यह भी देखें

- हार्डवेयर एक्सिलरेशन

- एआई त्वरक

- विशिष्ट एकीकृत परिपथ आवेदन

- क्षेत्र में प्रोग्राम की जा सकने वाली द्वार श्रंखला

श्रेणी:कंप्यूटर वास्तुकला