Difference between revisions of "एकीकृत सर्किट डिजाइन"

| Line 3: | Line 3: | ||

[[File:Vlsiopamp2.gif|400px|thumb|एक साधारण सीएमओएस ऑपरेशनल एम्पलीफायर का [[ एकीकृत सर्किट लेआउट ]] (इनपुट बाईं ओर हैं और मुआवजा संधारित्र दाईं ओर है)। धातु की परत नीले, हरे और भूरे रंग की होती है N- और P-doped Si, पॉलीसिलिकॉन लाल होता है और वायस क्रॉस होते हैं।]] | [[File:Vlsiopamp2.gif|400px|thumb|एक साधारण सीएमओएस ऑपरेशनल एम्पलीफायर का [[ एकीकृत सर्किट लेआउट ]] (इनपुट बाईं ओर हैं और मुआवजा संधारित्र दाईं ओर है)। धातु की परत नीले, हरे और भूरे रंग की होती है N- और P-doped Si, पॉलीसिलिकॉन लाल होता है और वायस क्रॉस होते हैं।]] | ||

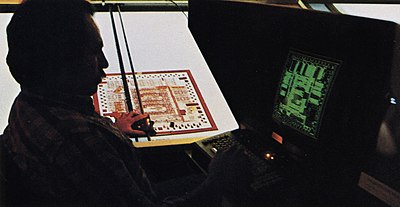

[[File:Integrated circuit designer Hughes Aircraft Company.jpg|thumb|400px|[[ रूबीलिथ ]] पर कटे हुए सर्किट डिज़ाइन के एक भाग का विश्लेषण करने के लिए एक प्रारंभिक आईसी-डिज़ाइनिंग वर्कस्टेशन का उपयोग करने वाला इंजीनियर, लगभग 1979]] | [[File:Integrated circuit designer Hughes Aircraft Company.jpg|thumb|400px|[[ रूबीलिथ ]] पर कटे हुए सर्किट डिज़ाइन के एक भाग का विश्लेषण करने के लिए एक प्रारंभिक आईसी-डिज़ाइनिंग वर्कस्टेशन का उपयोग करने वाला इंजीनियर, लगभग 1979]] | ||

इंटीग्रेटेड [[ सर्किट डिज़ाइन ]], या IC डिज़ाइन, [[ इलेक्ट्रॉनिक्स इंजीनियरिंग ]] का एक उप-क्षेत्र है, जिसमें [[ एकीकृत सर्किट ]] या IC को डिज़ाइन करने के लिए आवश्यक विशेष [[ बूलियन तर्क ]] और सर्किट डिज़ाइन तकनीक शामिल हैं। आईसी में [[ फोटोलिथोग्राफी ]] द्वारा मोनोलिथिक [[ सेमीकंडक्टर ]] सब्सट्रेट पर [[ विद्युत नेटवर्क ]] में निर्मित लघु [[ इलेक्ट्रॉनिक घटक ]] होते हैं। | इंटीग्रेटेड [[ सर्किट डिज़ाइन ]], या IC डिज़ाइन, [[ इलेक्ट्रॉनिक्स इंजीनियरिंग ]] का एक उप-क्षेत्र है, जिसमें [[ एकीकृत सर्किट ]] या IC को डिज़ाइन करने के लिए आवश्यक विशेष [[Index.php?title=बूलियन बीजगणित|बूलियन तर्क]] और सर्किट डिज़ाइन तकनीक शामिल हैं। आईसी में [[ फोटोलिथोग्राफी ]] द्वारा मोनोलिथिक [[ सेमीकंडक्टर ]] सब्सट्रेट पर [[ विद्युत नेटवर्क ]] में निर्मित लघु [[ इलेक्ट्रॉनिक घटक ]] होते हैं। | ||

आईसी डिजाइन को डिजिटल डेटा और [[ एनालॉग इलेक्ट्रॉनिक्स ]] आईसी डिजाइन की व्यापक श्रेणियों में विभाजित किया जा सकता है। डिजिटल आईसी डिजाइन [[ माइक्रोप्रोसेसरों ]], [[ एफपीजीए ]], मेमोरी ([[ यादृच्छिक अभिगम स्मृति ]], [[ रीड ऑनली मैमोरी ]] और [[ फ्लैश मेमोरी ]]) और डिजिटल एप्लिकेशन-विशिष्ट एकीकृत सर्किट जैसे घटकों का उत्पादन करना है। डिजिटल डिजाइन तार्किक शुद्धता, सर्किट घनत्व को अधिकतम करने और सर्किट रखने पर केंद्रित है ताकि घड़ी और समय संकेतों को कुशलता से रूट किया जा सके। एनालॉग आईसी डिजाइन में पावर आईसी डिजाइन और [[ आकाशवाणी आवृति ]] आईसी डिजाइन में विशेषज्ञता भी है। एनालॉग आईसी डिज़ाइन का उपयोग [[ op-amp ]]s, [[ रैखिक नियामक ]], [[ चरण बंद लूप ]], [[ थरथरानवाला ]] और [[ सक्रिय फ़िल्टर ]] के डिज़ाइन में किया जाता है। एनालॉग डिजाइन अर्धचालक उपकरणों जैसे लाभ, मिलान, बिजली अपव्यय और प्रतिरोध के भौतिकी से अधिक चिंतित है। एनालॉग सिग्नल एम्प्लीफिकेशन और फ़िल्टरिंग की निष्ठा आमतौर पर महत्वपूर्ण होती है और इसके परिणामस्वरूप, एनालॉग आईसी डिजिटल डिज़ाइन की तुलना में बड़े क्षेत्र के सक्रिय उपकरणों का उपयोग करते हैं और आमतौर पर सर्किटरी में कम घने होते हैं। | आईसी डिजाइन को डिजिटल डेटा और [[ एनालॉग इलेक्ट्रॉनिक्स ]] आईसी डिजाइन की व्यापक श्रेणियों में विभाजित किया जा सकता है। डिजिटल आईसी डिजाइन [[ माइक्रोप्रोसेसरों ]], [[ एफपीजीए ]], मेमोरी ([[ यादृच्छिक अभिगम स्मृति ]], [[ रीड ऑनली मैमोरी ]] और [[ फ्लैश मेमोरी ]]) और डिजिटल एप्लिकेशन-विशिष्ट एकीकृत सर्किट जैसे घटकों का उत्पादन करना है। डिजिटल डिजाइन तार्किक शुद्धता, सर्किट घनत्व को अधिकतम करने और सर्किट रखने पर केंद्रित है ताकि घड़ी और समय संकेतों को कुशलता से रूट किया जा सके। एनालॉग आईसी डिजाइन में पावर आईसी डिजाइन और [[ आकाशवाणी आवृति ]] आईसी डिजाइन में विशेषज्ञता भी है। एनालॉग आईसी डिज़ाइन का उपयोग [[ op-amp ]]s, [[ रैखिक नियामक ]], [[ चरण बंद लूप ]], [[ थरथरानवाला ]] और [[ सक्रिय फ़िल्टर ]] के डिज़ाइन में किया जाता है। एनालॉग डिजाइन अर्धचालक उपकरणों जैसे लाभ, मिलान, बिजली अपव्यय और प्रतिरोध के भौतिकी से अधिक चिंतित है। एनालॉग सिग्नल एम्प्लीफिकेशन और फ़िल्टरिंग की निष्ठा आमतौर पर महत्वपूर्ण होती है और इसके परिणामस्वरूप, एनालॉग आईसी डिजिटल डिज़ाइन की तुलना में बड़े क्षेत्र के सक्रिय उपकरणों का उपयोग करते हैं और आमतौर पर सर्किटरी में कम घने होते हैं। | ||

Revision as of 13:00, 1 September 2022

This article includes a list of general references, but it lacks sufficient corresponding inline citations. (March 2019) (Learn how and when to remove this template message) |

इंटीग्रेटेड सर्किट डिज़ाइन , या IC डिज़ाइन, इलेक्ट्रॉनिक्स इंजीनियरिंग का एक उप-क्षेत्र है, जिसमें एकीकृत सर्किट या IC को डिज़ाइन करने के लिए आवश्यक विशेष बूलियन तर्क और सर्किट डिज़ाइन तकनीक शामिल हैं। आईसी में फोटोलिथोग्राफी द्वारा मोनोलिथिक सेमीकंडक्टर सब्सट्रेट पर विद्युत नेटवर्क में निर्मित लघु इलेक्ट्रॉनिक घटक होते हैं।

आईसी डिजाइन को डिजिटल डेटा और एनालॉग इलेक्ट्रॉनिक्स आईसी डिजाइन की व्यापक श्रेणियों में विभाजित किया जा सकता है। डिजिटल आईसी डिजाइन माइक्रोप्रोसेसरों , एफपीजीए , मेमोरी (यादृच्छिक अभिगम स्मृति , रीड ऑनली मैमोरी और फ्लैश मेमोरी ) और डिजिटल एप्लिकेशन-विशिष्ट एकीकृत सर्किट जैसे घटकों का उत्पादन करना है। डिजिटल डिजाइन तार्किक शुद्धता, सर्किट घनत्व को अधिकतम करने और सर्किट रखने पर केंद्रित है ताकि घड़ी और समय संकेतों को कुशलता से रूट किया जा सके। एनालॉग आईसी डिजाइन में पावर आईसी डिजाइन और आकाशवाणी आवृति आईसी डिजाइन में विशेषज्ञता भी है। एनालॉग आईसी डिज़ाइन का उपयोग op-amp s, रैखिक नियामक , चरण बंद लूप , थरथरानवाला और सक्रिय फ़िल्टर के डिज़ाइन में किया जाता है। एनालॉग डिजाइन अर्धचालक उपकरणों जैसे लाभ, मिलान, बिजली अपव्यय और प्रतिरोध के भौतिकी से अधिक चिंतित है। एनालॉग सिग्नल एम्प्लीफिकेशन और फ़िल्टरिंग की निष्ठा आमतौर पर महत्वपूर्ण होती है और इसके परिणामस्वरूप, एनालॉग आईसी डिजिटल डिज़ाइन की तुलना में बड़े क्षेत्र के सक्रिय उपकरणों का उपयोग करते हैं और आमतौर पर सर्किटरी में कम घने होते हैं।

आधुनिक आईसी बेहद जटिल हैं। 2015 तक एक औसत डेस्कटॉप कंप्यूटर चिप में 1 बिलियन से अधिक ट्रांजिस्टर हैं। क्या बनाया जा सकता है और क्या नहीं, इसके लिए डिजाइन नियम भी बेहद जटिल हैं। 2015 की सामान्य आईसी प्रक्रियाओं में 500 से अधिक नियम हैं। इसके अलावा, चूंकि निर्माण प्रक्रिया स्वयं पूरी तरह से अनुमानित नहीं है, इसलिए डिजाइनरों को इसकी सांख्यिकी प्रकृति के लिए जिम्मेदार होना चाहिए। आधुनिक आईसी डिजाइन की जटिलता, साथ ही तेजी से डिजाइन तैयार करने के लिए बाजार के दबाव ने आईसी डिजाइन प्रक्रिया में इलेक्ट्रॉनिक डिजाइन स्वचालन के व्यापक उपयोग को प्रेरित किया है। संक्षेप में, इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन का उपयोग करते हुए एक IC का डिज़ाइन निर्देशों का डिज़ाइन, परीक्षण और सत्यापन है जिसे IC को पूरा करना है।

बुनियादी बातें

इंटीग्रेटेड सर्किट डिज़ाइन में इलेक्ट्रॉनिक घटकों, जैसे ट्रांजिस्टर , रेसिस्टर्स, संधारित्र और इन घटकों के इंटरकनेक्ट्स (एकीकृत सर्किट) को सेमीकंडक्टर, आमतौर पर सिलिकॉन के एक टुकड़े पर बनाना शामिल है। वेफर (इलेक्ट्रॉनिक्स) में बने व्यक्तिगत घटकों को अलग करने की एक विधि आवश्यक है क्योंकि सब्सट्रेट सिलिकॉन प्रवाहकीय है और अक्सर व्यक्तिगत घटकों का एक सक्रिय क्षेत्र बनाता है। दो सामान्य तरीके पी-एन जंक्शन अलगाव और ढांकता हुआ अलगाव हैं। ट्रांजिस्टर के बिजली अपव्यय और इंटरकनेक्ट प्रतिरोधों और इंटरकनेक्ट के वर्तमान घनत्व पर ध्यान दिया जाना चाहिए, वाया (इलेक्ट्रॉनिक्स) क्योंकि आईसी में असतत घटकों की तुलना में बहुत छोटे उपकरण होते हैं, जहां ऐसी चिंताएं कम होती हैं। मेटलिक इंटरकनेक्ट में इलेक्ट्रोमाइग्रेशन और छोटे घटकों को स्थिरविद्युत निर्वाह क्षति भी चिंता का विषय है। अंत में, कुछ सर्किट सबब्लॉक का भौतिक लेआउट आम तौर पर महत्वपूर्ण होता है, ऑपरेशन की वांछित गति प्राप्त करने के लिए, शांत भागों से आईसी के शोर भागों को अलग करने के लिए, आईसी भर में गर्मी उत्पादन के प्रभाव को संतुलित करने के लिए, या प्लेसमेंट (ईडीए) सुविधा के लिए। (EDA) आईसी के बाहर सर्किटरी के कनेक्शन।

डिजाइन प्रवाह

एक विशिष्ट आईसी डिजाइन चक्र में कई चरण शामिल हैं:

- सिस्टम विशिष्टता

- व्यवहार्यता अध्ययन और मरने के आकार का अनुमान

- फ़ंक्शन विश्लेषण

- आर्किटेक्चरल या सिस्टम लेवल डिज़ाइन

- तर्क डिजाइन

- एनालॉग डिजाइन, सिमुलेशन और लेआउट

- डिजिटल डिजाइन और सिमुलेशन

- सिस्टम सिमुलेशन और सत्यापन

- सर्किट डिज़ाइन

- डिजिटल डिजाइन संश्लेषण

- टेस्ट के लिए डिजाइन और स्वचालित परीक्षण पैटर्न पीढ़ी

- निर्माण क्षमता के लिए डिजाइन (आईसी)

- भौतिक डिजाइन

- फर्श योजना

- स्थान और मार्ग

- परजीवी निष्कर्षण

- भौतिक सत्यापन और साइनऑफ़ (इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन)

- स्थिर समय

- सह-सिमुलेशन और समय

- मास्क डेटा तैयार करना (लेआउट पोस्ट प्रोसेसिंग)

- चिपचिपा रकम गंवाना; मर जाना के साथ परिष्करण

- रेटिकल लेआउट

- लेआउट-टू-मास्क तैयारी

- सेमीकंडक्टर निर्माण

- एकीकृत सर्किट पैकेजिंग

- वेफर परीक्षण

- सिलिकॉन सत्यापन और एकीकरण पोस्ट करें

- डिवाइस विशेषता

- ट्वीक (यदि आवश्यक हो)

- चिप परिनियोजन

- डेटाशीट पीढ़ी (आमतौर पर एक पोर्टेबल दस्तावेज़ प्रारूप (पीडीएफ) फ़ाइल की)

- बढ़ाना

- उत्पादन

- यील्ड विश्लेषण / वारंटी विश्लेषण विश्वसनीयता (अर्धचालक)

- किसी भी रिटर्न पर विफलता विश्लेषण

- यदि संभव हो तो उत्पादन जानकारी का उपयोग करके अगली पीढ़ी के चिप की योजना बनाएं

सारांश

मोटे तौर पर कहें तो डिजिटल आईसी डिजाइन को तीन भागों में बांटा जा सकता है।

- इलेक्ट्रॉनिक सिस्टम-स्तर ीय डिज़ाइन: यह चरण उपयोगकर्ता के कार्यात्मक विनिर्देश बनाता है। इस विवरण को बनाने के लिए उपयोगकर्ता विभिन्न भाषाओं और उपकरणों का उपयोग कर सकता है। उदाहरणों में C (प्रोग्रामिंग भाषा)/C++ मॉडल, VHDL , SystemC , SystemVerilog लेन-देन-स्तर मॉडलिंग , Simulink और MATLAB शामिल हैं।

- RTL डिज़ाइन: यह चरण उपयोगकर्ता विनिर्देश (उपयोगकर्ता जो चिप को करना चाहता है) को एक रजिस्टर स्थानांतरण स्तर (RTL) विवरण में परिवर्तित करता है। आरटीएल चिप पर डिजिटल सर्किट के सटीक व्यवहार के साथ-साथ इनपुट और आउटपुट के इंटरकनेक्शन का वर्णन करता है।

- भौतिक डिजाइन (इलेक्ट्रॉनिक्स) : यह कदम आरटीएल, और उपलब्ध लॉजिक गेट्स (मानक सेल लाइब्रेरी) की एक लाइब्रेरी लेता है, और एक चिप डिजाइन बनाता है। इस चरण में आईसी लेआउट संपादक , लेआउट और फ्लोर प्लानिंग का उपयोग शामिल है, यह पता लगाना कि किस गेट का उपयोग करना है, उनके लिए स्थानों को परिभाषित करना और उन्हें एक साथ वायरिंग (घड़ी का समय संश्लेषण, रूटिंग) करना है।

ध्यान दें कि दूसरा चरण, RTL डिज़ाइन, चिप के सही काम करने के लिए ज़िम्मेदार है। तीसरा चरण, भौतिक डिज़ाइन, कार्यक्षमता को बिल्कुल भी प्रभावित नहीं करता है (यदि सही तरीके से किया जाता है) लेकिन यह निर्धारित करता है कि चिप कितनी तेजी से संचालित होती है और इसकी लागत कितनी है।

डिजाइन जीवनचक्र

एकीकृत सर्किट (आईसी) विकास प्रक्रिया उत्पाद आवश्यकताओं को परिभाषित करने के साथ शुरू होती है, वास्तुशिल्प परिभाषा, कार्यान्वयन, लाने और अंत में उत्पादन के माध्यम से आगे बढ़ती है। एकीकृत परिपथ विकास प्रक्रिया के विभिन्न चरणों का वर्णन नीचे किया गया है। हालाँकि चरणों को यहाँ सीधे-सीधे तरीके से प्रस्तुत किया गया है, वास्तव में पुनरावृत्ति होती है और ये चरण कई बार हो सकते हैं।

आवश्यकताएँ

एक वास्तुकला को परिभाषित करने से पहले कुछ उच्च स्तरीय उत्पाद लक्ष्यों को परिभाषित किया जाना चाहिए। आवश्यकताएं आमतौर पर एक क्रॉस फंक्शनल टीम द्वारा उत्पन्न की जाती हैं जो बाजार के अवसर, ग्राहक की जरूरतों, विक्षनरी: व्यवहार्यता और बहुत कुछ को संबोधित करती है। इस चरण का परिणाम उत्पाद आवश्यकताओं के दस्तावेज़ में होना चाहिए।

वास्तुकला

वास्तुकला उत्पाद की मौलिक संरचना, लक्ष्यों और सिद्धांतों को परिभाषित करता है। यह उच्च स्तरीय अवधारणाओं और उत्पाद के आंतरिक मूल्य प्रस्ताव को परिभाषित करता है। आर्किटेक्चर टीम कई समूहों के साथ कई चर और इंटरफेस को ध्यान में रखती है। आर्किटेक्चर बनाने वाले लोगों के पास आमतौर पर उस क्षेत्र में सिस्टम से निपटने का एक महत्वपूर्ण अनुभव होता है जिसके लिए आर्किटेक्चर बनाया जा रहा है। वास्तुकला चरण का कार्य उत्पाद एक वास्तुशिल्प विनिर्देश है।

माइक्रो-आर्किटेक्चर

माइक्रो-आर्किटेक्चर हार्डवेयर के करीब एक कदम है। यह वास्तुकला को लागू करता है और उस कार्यान्वयन को प्राप्त करने के लिए विशिष्ट तंत्र और संरचनाओं को परिभाषित करता है। माइक्रो-आर्किटेक्चर चरण का परिणाम एक माइक्रो-आर्किटेक्चर विनिर्देश है जो आर्किटेक्चर को लागू करने के लिए उपयोग की जाने वाली विधियों का वर्णन करता है।

कार्यान्वयन

कार्यान्वयन चरण में प्रारंभिक बिंदु के रूप में सूक्ष्म-वास्तुशिल्प विनिर्देश का उपयोग करके डिजाईन स्वयं बनाया जाता है। इसमें निम्न स्तर की परिभाषा और विभाजन, कोड लिखना, योजनाबद्ध और सत्यापन दर्ज करना शामिल है। यह चरण रकम गंवाना; मर जाना तक पहुंचने वाले डिज़ाइन के साथ समाप्त होता है।

ब्रिंगअप

एक डिज़ाइन तैयार होने के बाद, टेप-आउट और निर्मित, वास्तविक हार्डवेयर, 'पहला सिलिकॉन' प्राप्त होता है, जिसे प्रयोगशाला में ले जाया जाता है जहां इसे लाया जाता है। ब्रिंगअप प्रयोगशाला में डिजाइन को सशक्त बनाने, परीक्षण करने और उसकी विशेषता बताने की प्रक्रिया है। बहुत ही सरल परीक्षणों से शुरू होकर कई गुणवत्ता नियंत्रण किए जाते हैं जैसे कि यह सुनिश्चित करना कि उपकरण बहुत अधिक जटिल परीक्षणों को शक्ति देगा जो विभिन्न तरीकों से भाग पर जोर देने का प्रयास करते हैं। लाने के चरण का परिणाम लक्षण वर्णन डेटा का प्रलेखन है (भाग कल्पना के लिए कितना अच्छा प्रदर्शन करता है) और इरेटा (अप्रत्याशित व्यवहार)।

उत्पादन

उत्पादीकरण इंजीनियरिंग से बड़े पैमाने पर उत्पादन निर्माण में एक डिजाइन लेने का कार्य है। यद्यपि एक डिज़ाइन ने प्रयोगशाला में उत्पाद के विनिर्देशों को सफलतापूर्वक पूरा किया हो सकता है, लेकिन उन डिज़ाइनों का बड़े पैमाने पर उत्पादन करने की कोशिश करते समय उत्पाद इंजीनियरों को कई चुनौतियों का सामना करना पड़ता है। एकीकृत सर्किट को स्वीकार्य उपज के साथ उत्पादन मात्रा तक बढ़ाया जाना चाहिए। उत्पादीकरण चरण का लक्ष्य स्वीकार्य लागत पर बड़े पैमाने पर उत्पादन की मात्रा तक पहुंचना है।

सतत

एक बार जब कोई डिज़ाइन परिपक्व हो जाता है और बड़े पैमाने पर उत्पादन तक पहुँच जाता है तो उसे बनाए रखना चाहिए। उत्पादन की मात्रा पर एक महत्वपूर्ण प्रभाव से बचने के लिए प्रक्रिया की लगातार निगरानी की जानी चाहिए और समस्याओं से शीघ्रता से निपटा जाना चाहिए। बनाए रखने का लक्ष्य उत्पादन की मात्रा को बनाए रखना और उत्पाद के जीवन के अंत (उत्पाद) तक पहुंचने तक लागत को लगातार कम करना है।

डिजाइन प्रक्रिया

माइक्रोआर्किटेक्चर और सिस्टम-स्तरीय डिज़ाइन

प्रारंभिक चिप डिजाइन प्रक्रिया सिस्टम-स्तरीय डिजाइन और माइक्रोआर्किटेक्चर योजना के साथ शुरू होती है। आईसी डिजाइन कंपनियों के भीतर, प्रबंधन और अक्सर एनालिटिक्स एक डिजाइन टीम के लिए एक उद्योग खंड में फिट होने के लिए एक नई चिप के डिजाइन को शुरू करने के लिए एक प्रस्ताव का मसौदा तैयार करेंगे। चिप कैसे कार्यात्मक रूप से काम करेगी, यह तय करने के लिए ऊपरी स्तर के डिजाइनर इस स्तर पर मिलेंगे। यह कदम वह जगह है जहां एक आईसी की कार्यक्षमता और डिजाइन तय की जाती है। आईसी डिजाइनर पूरी परियोजना के लिए कार्यात्मक आवश्यकताओं, सत्यापन टेस्टबेंच और परीक्षण पद्धतियों का नक्शा तैयार करेंगे, और फिर प्रारंभिक डिजाइन को सिस्टम-स्तरीय विनिर्देश में बदल देंगे जिसे सी ++ और MATLAB और इम्यूलेशन टूल्स जैसी भाषाओं का उपयोग करके सरल मॉडल के साथ अनुकरण किया जा सकता है। शुद्ध और नए डिज़ाइनों के लिए, सिस्टम डिज़ाइन चरण वह है जहाँ एक निर्देश सेट और संचालन की योजना बनाई जाती है, और अधिकांश चिप्स में मौजूदा निर्देश सेट को नई कार्यक्षमता के लिए संशोधित किया जाता है। इस स्तर पर डिजाइन अक्सर बयान होते हैं जैसे बेचा 3 प्रारूप में एन्कोड या आईईईई फ्लोटिंग-पॉइंट अंकगणित लागू करता है। डिजाइन प्रक्रिया में बाद के चरणों में, इन निर्दोष दिखने वाले बयानों में से प्रत्येक का विस्तार पाठ्य प्रलेखन के सैकड़ों पृष्ठों तक होता है।

आरटीएल डिजाइन

सिस्टम डिज़ाइन के समझौते पर, RTL डिज़ाइनर तब कार्यात्मक मॉडल को हार्डवेयर विवरण भाषा जैसे Verilog , SystemVerilog, या VHDL में लागू करते हैं। एडर्स, शिफ्टर्स, और स्टेट मशीन जैसे डिजिटल डिज़ाइन घटकों के साथ-साथ कंप्यूटर आर्किटेक्चर अवधारणाओं जैसे पाइपलाइनिंग, सुपरस्केलर निष्पादन और शाखा भविष्यवाणी का उपयोग करते हुए, आरटीएल डिजाइनर एक साथ काम करने वाले चिप पर घटकों के हार्डवेयर मॉडल में एक कार्यात्मक विवरण को तोड़ देंगे। सिस्टम डिजाइन में वर्णित प्रत्येक सरल कथन आसानी से रजिस्टर-स्थानांतरण स्तर कोड की हजारों पंक्तियों में बदल सकता है, यही कारण है कि यह सत्यापित करना बेहद मुश्किल है कि आरटीएल उन सभी संभावित मामलों में सही काम करेगा जो उपयोगकर्ता कर सकते हैं उस पर फेंको।

कार्यात्मक बग की संख्या को कम करने के लिए, एक अलग हार्डवेयर सत्यापन समूह आरटीएल और डिजाइन टेस्टबेंच और सिस्टम को यह जांचने के लिए लेगा कि आरटीएल वास्तव में कार्यात्मक सत्यापन के डोमेन के रूप में वर्गीकृत कई अलग-अलग परिस्थितियों में एक ही चरण का प्रदर्शन कर रहा है। कई तकनीकों का उपयोग किया जाता है, उनमें से कोई भी सही नहीं है, लेकिन वे सभी उपयोगी हैं - व्यापक तर्क सिमुलेशन, औपचारिक तरीके , हार्डवेयर अनुकरण , लिंट प्रोग्रामिंग टूल -जैसे कोड जांच, कोड कवरेज़ , और इसी तरह।

यहां एक छोटी सी त्रुटि पूरी चिप को बेकार या खराब कर सकती है। प्रसिद्ध पेंटियम FDIV बग के कारण विभाजन के परिणाम प्रति मिलियन अधिकतम 61 भागों में गलत हो गए, ऐसे मामलों में जो बहुत कम होते थे। महीनों तक चिप का उत्पादन होने तक किसी ने इस पर ध्यान भी नहीं दिया। फिर भी इंटेल को 475 मिलियन डॉलर (यूएस) की लागत से, बग को ठीक करने तक बेची जाने वाली प्रत्येक चिप को मुफ्त में बदलने की पेशकश करने के लिए मजबूर होना पड़ा।[citation needed]

भौतिक डिजाइन

आरटीएल केवल उस वास्तविक कार्यक्षमता का एक व्यवहार मॉडल है जिसके तहत चिप को संचालित करना चाहिए। इसका भौतिक पहलू से कोई संबंध नहीं है कि सामग्री, भौतिकी और इलेक्ट्रिकल इंजीनियरिंग पक्ष में वास्तविक जीवन में चिप कैसे काम करेगी। इस कारण से, IC डिज़ाइन प्रक्रिया में अगला चरण, भौतिक डिज़ाइन (इलेक्ट्रॉनिक्स) चरण, RTL को सभी इलेक्ट्रॉनिक उपकरणों, जैसे कैपेसिटर, रेसिस्टर्स, लॉजिक गेट्स, और ट्रांजिस्टर के वास्तविक ज्यामितीय प्रतिनिधित्व में मैप करना है, जो चालू होगा। टुकड़ा।

भौतिक डिजाइन के मुख्य चरण नीचे सूचीबद्ध हैं। व्यवहार में कोई सीधी प्रगति नहीं है - सभी उद्देश्यों को एक साथ पूरा करने के लिए काफी पुनरावृत्ति की आवश्यकता होती है। यह अपने आप में एक कठिन समस्या है, जिसे डिजाइन बंद करना कहा जाता है।

- तर्क संश्लेषण : चिप की लक्ष्य प्रौद्योगिकी में आरटीएल को गेट-स्तरीय नेटलिस्ट में मैप किया जाता है।

- फ्लोरप्लान (माइक्रोइलेक्ट्रॉनिक्स) : चिप का आरटीएल चिप के सकल क्षेत्रों को सौंपा गया है, इनपुट/आउटपुट (आई/ओ) पिन असाइन किए गए हैं और बड़ी वस्तुएं (सरणी, कोर, आदि) रखी गई हैं।

- प्लेसमेंट (ईडीए): नेटलिस्ट में गेट्स को डाई क्षेत्र पर गैर-अतिव्यापी स्थानों को सौंपा गया है।

- तर्क/नियुक्ति शोधन: प्रदर्शन और शक्ति बाधाओं को बंद करने के लिए पुनरावृत्त तार्किक और प्लेसमेंट परिवर्तन।

- घड़ी वितरण नेटवर्क : क्लॉक सिग्नल वायरिंग (आमतौर पर, घड़ी का पेड़ ) को डिजाइन में पेश किया जाता है।

- रूटिंग (ईडीए) : नेटलिस्ट में फाटकों को जोड़ने वाले तार जोड़े जाते हैं।

- पोस्टवायरिंग अनुकूलन: प्रदर्शन (समय बंद), शोर (सिग्नल अखंडता), और उपज (डिजाइन फॉर मैन्युफैक्चरिबिलिटी (आईसी)) उल्लंघन हटा दिए जाते हैं।

- निर्माण के लिए डिजाइन (आईसी): डिजाइन को संशोधित किया जाता है, जहां संभव हो, इसे उत्पादन के लिए जितना संभव हो उतना आसान और कुशल बनाने के लिए। यह फाउंड्री द्वारा निर्धारित डिजाइन नियमों का पालन करते हुए जहां भी संभव हो, अतिरिक्त वायस जोड़कर या डमी मेटल/डिफ्यूजन/पॉली लेयर्स जोड़कर हासिल किया जाता है।

- अंतिम जांच: चूंकि त्रुटियां महंगी, समय लेने वाली और पहचान में मुश्किल होती हैं, इसलिए व्यापक त्रुटि जांच नियम, औपचारिक समकक्ष जांच और डिजाइन नियम जांच है।

- टेप-आउट और मास्क जनरेशन के साथ चिप फिनिशिंग: मास्क डेटा तैयार करने में डिज़ाइन डेटा को फोटोमास्क में बदल दिया जाता है।[1]

एनालॉग डिजाइन

माइक्रोप्रोसेसर और सॉफ्टवेयर आधारित डिजाइन टूल के आगमन से पहले, एनालॉग आईसी को हाथ की गणना और प्रक्रिया किट भागों का उपयोग करके डिजाइन किया गया था। ये IC कम जटिलता वाले सर्किट थे, उदाहरण के लिए, op-amps, जिसमें आमतौर पर दस से अधिक ट्रांजिस्टर और कुछ कनेक्शन शामिल नहीं होते थे। एक निर्माण योग्य आईसी प्राप्त करने के लिए एक पुनरावृत्त परीक्षण और त्रुटि प्रक्रिया और डिवाइस आकार की ओवरइंजीनियरिंग अक्सर आवश्यक होती थी। सिद्ध डिजाइनों के पुन: उपयोग ने पूर्व ज्ञान पर उत्तरोत्तर अधिक जटिल आईसी बनाने की अनुमति दी। जब 1970 के दशक में सस्ती कंप्यूटर प्रोसेसिंग उपलब्ध हो गई, तो हाथ की गणना द्वारा व्यावहारिक की तुलना में अधिक सटीकता के साथ सर्किट डिजाइनों का अनुकरण करने के लिए कंप्यूटर प्रोग्राम लिखे गए। एनालॉग आईसी के लिए पहले सर्किट सिम्युलेटर को मसाला (एकीकृत सर्किट जोर के साथ सिमुलेशन प्रोग्राम) कहा जाता था। कम्प्यूटरीकृत सर्किट सिमुलेशन उपकरण हाथ की गणना की तुलना में अधिक आईसी डिजाइन जटिलता को सक्षम करते हैं, एनालॉग एप्लिकेशन-विशिष्ट एकीकृत सर्किट के डिजाइन को व्यावहारिक बनाते हैं।

एनालॉग डिजाइन में कई कार्यात्मक बाधाओं पर विचार किया जाना चाहिए, मैनुअल डिजाइन आज भी व्यापक है। नतीजतन, एनालॉग सर्किट के लिए आधुनिक डिजाइन प्रवाह दो अलग-अलग डिजाइन शैलियों की विशेषता है - ऊपर-नीचे और नीचे-ऊपर।[2] टॉप-डाउन डिज़ाइन शैली पारंपरिक डिजिटल प्रवाह के समान अनुकूलन-आधारित टूल का उपयोग करती है। बॉटम-अप प्रक्रियाएं "विशेषज्ञ ज्ञान" का पुन: उपयोग करती हैं, जो एक विशेषज्ञ के निर्णय की नकल करते हुए पहले से कल्पना की गई और प्रक्रियात्मक विवरण में कैप्चर किए गए समाधानों के परिणाम के साथ होती हैं।[2]एक उदाहरण सेल जनरेटर हैं, जैसे कि PCell s।

परिवर्तनशीलता से मुकाबला

एनालॉग आईसी डिजाइन के लिए सबसे महत्वपूर्ण चुनौती में सेमीकंडक्टर चिप पर निर्मित व्यक्तिगत उपकरणों की परिवर्तनशीलता शामिल है। बोर्ड-स्तरीय सर्किट डिज़ाइन के विपरीत, जो डिज़ाइनर को उन उपकरणों का चयन करने की अनुमति देता है, जिनमें से प्रत्येक का परीक्षण किया गया है और मूल्य के अनुसार बिन किया गया है, एक IC पर डिवाइस मान व्यापक रूप से भिन्न हो सकते हैं जो डिज़ाइनर द्वारा बेकाबू होते हैं। उदाहरण के लिए, कुछ आईसी प्रतिरोधक ±20% भिन्न हो सकते हैं और एक एकीकृत द्विध्रुवीय द्विध्रुवी जंक्शन ट्रांजिस्टर β 20 से 100 तक भिन्न हो सकता है। नवीनतम सीएमओएस प्रक्रियाओं में, लंबवत पीएनपी ट्रांजिस्टर के β नीचे भी जा सकते हैं। डिजाइन चुनौती में जोड़ने के लिए, प्रत्येक संसाधित अर्धचालक वेफर के बीच उपकरण गुण अक्सर भिन्न होते हैं। डोपिंग ढ़ाल के कारण प्रत्येक व्यक्तिगत आईसी में डिवाइस के गुण भी काफी भिन्न हो सकते हैं। इस परिवर्तनशीलता का अंतर्निहित कारण यह है कि कई अर्धचालक उपकरण प्रक्रिया में अनियंत्रित यादृच्छिक भिन्नताओं के प्रति अत्यधिक संवेदनशील होते हैं। प्रसार समय की मात्रा में थोड़ा सा परिवर्तन, असमान डोपिंग स्तर, आदि का डिवाइस के गुणों पर बड़ा प्रभाव पड़ सकता है।

डिवाइस भिन्नता के प्रभावों को कम करने के लिए उपयोग की जाने वाली कुछ डिज़ाइन तकनीकें हैं:[3]

- प्रतिरोधों के अनुपातों का उपयोग करना, जो पूर्ण प्रतिरोधक मान के बजाय निकटता से मेल खाते हैं।

- मिलान वाली ज्यामितीय आकृतियों वाले उपकरणों का उपयोग करना ताकि वे विविधताओं से मेल खाते हों।

- उपकरणों को बड़ा बनाना ताकि सांख्यिकीय भिन्नता समग्र उपकरण संपत्ति का एक महत्वहीन अंश बन जाए।

- प्रतिरोधों जैसे बड़े उपकरणों को भागों में विभाजित करना और विविधताओं को रद्द करने के लिए उन्हें आपस में जोड़ना।

- उन उपकरणों में भिन्नताओं को रद्द करने के लिए सामान्य सेंट्रोइड डिवाइस लेआउट का उपयोग करना जो बारीकी से मेल खाना चाहिए (जैसे कि एक सेशन amp की ट्रांजिस्टर अंतर जोड़ी)।

विक्रेता

इलेक्ट्रॉनिक डिज़ाइन ऑटोमेशन टूल बेचने वाली तीन सबसे बड़ी कंपनियाँ हैं Synopsys , Cadence Design Systems और Mentor ग्राफ़िक्स।[4]

यह भी देखें

- इलेक्ट्रॉनिक सर्किट डिजाइन

- इलेक्ट्रॉनिक डिजाइन स्वचालन

- पावर नेटवर्क डिजाइन (आईसी)

- प्रोसेसर डिजाइन

- इंटीग्रेटेड सर्किट और सिस्टम के कंप्यूटर एडेड डिजाइन पर आईईईई लेनदेन

- बहु-परियोजना वेफर सेवा

- मानक सेल

संदर्भ

- ↑ J. Lienig, J. Scheible (2020). "Chap. 3.3: Mask Data: Layout Post Processing". Fundamentals of Layout Design for Electronic Circuits. Springer. pp. 102–110. doi:10.1007/978-3-030-39284-0. ISBN 978-3-030-39284-0. S2CID 215840278.

- ↑ 2.0 2.1 J. Lienig, J. Scheible (2020). "Chap. 4.6: Analog and Digital Design Flows". Fundamentals of Layout Design for Electronic Circuits. Springer. pp. 151–159. doi:10.1007/978-3-030-39284-0. ISBN 978-3-030-39284-0. S2CID 215840278.

- ↑ Basu, Joydeep (2019-10-09). "From Design to Tape-out in SCL 180 nm CMOS Integrated Circuit Fabrication Technology". IETE Journal of Education. 60 (2): 51–64. arXiv:1908.10674. doi:10.1080/09747338.2019.1657787. S2CID 201657819.

- ↑ "Developments of Multi-CAD Models" (PDF). IC CAD Market Trends 2015. 2015-07-11.

इस पृष्ठ में अनुपलब्ध आंतरिक कड़ियों की सूची

- आंकड़े

- डिजिटल डाटा

- विशिष्ट एकीकृत परिपथ आवेदन

- के माध्यम से (इलेक्ट्रॉनिक्स)

- असफलता विश्लेषण

- मास्क डेटा तैयारी

- संवहन दस्तावेज़ स्वरूप

- विनिर्माण क्षमता के लिए डिजाइन (आईसी)

- सिलिकॉन सत्यापन पोस्ट करें

- रजिस्टर ट्रांसफर लेवल

- सी (प्रोग्रामिंग भाषा)

- यात्रा

- मांग

- बाज़ार अवसर

- उत्पाद आवश्यकता दस्तावेज़

- जीवन का अंत (उत्पाद)

- निर्देश समुच्चय

- तर्क अनुकरण

- टाइमिंग क्लोजर

- औपचारिक तुल्यता जाँच

- डिजाइन नियम की जाँच

- सिग्नल की समग्रता

- ऑप एंप

- सामान्य केन्द्रक

- मेंटर ग्राफिक्स

- एकीकृत परिपथों और प्रणालियों के कंप्यूटर सहायता प्राप्त डिजाइन पर आईईईई लेनदेन

अग्रिम पठन

- Electronic Design Automation For Integrated Circuits Handbook, by Lavagno, Martin, and Scheffer, ISBN 0-8493-3096-3 A survey of the field of electronic design automation, one of the main enablers of modern IC design.