एडीसी को एकीकृत करना

This article needs additional citations for verification. (May 2022) (Learn how and when to remove this template message) |

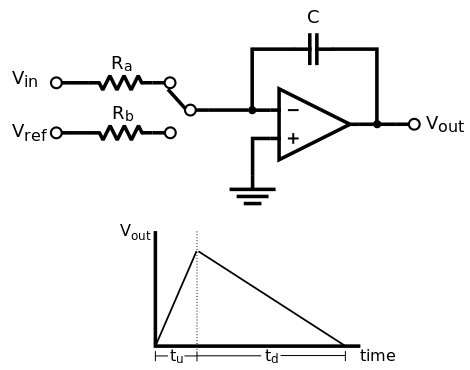

एक एकीकृत एडीसी एक प्रकार का एनॉलॉग से डिजिटल परिवर्तित करने वाला उपकरण है जो एक परिचालन एम्पलीफायर अनुप्रयोगों # इन्वर्टिंग इंटीग्रेटर के उपयोग के माध्यम से एक अज्ञात इनपुट वोल्टेज को डिजिटल प्रतिनिधित्व में परिवर्तित करता है। इसके मूल कार्यान्वयन में, दोहरे ढलान वाला कनवर्टर, अज्ञात इनपुट वोल्टेज को इंटीग्रेटर के इनपुट पर लागू किया जाता है और एक निश्चित समय अवधि (रन-अप अवधि) के लिए रैंप की अनुमति दी जाती है। फिर विपरीत ध्रुवता के ज्ञात संदर्भ वोल्टेज को इंटीग्रेटर पर लागू किया जाता है और जब तक इंटीग्रेटर आउटपुट शून्य (रन-डाउन अवधि) पर वापस नहीं आ जाता तब तक रैंप की अनुमति दी जाती है। इनपुट वोल्टेज की गणना संदर्भ वोल्टेज, निरंतर रन-अप समय अवधि और मापा रन-डाउन समय अवधि के एक समारोह के रूप में की जाती है। रन-डाउन टाइम मापन आमतौर पर कनवर्टर की घड़ी की इकाइयों में किया जाता है, इसलिए लंबे समय तक एकीकरण समय उच्च रिज़ॉल्यूशन की अनुमति देता है। इसी तरह, संकल्प त्याग कर कनवर्टर की गति में सुधार किया जा सकता है।

इस प्रकार के कन्वर्टर्स उच्च रिज़ॉल्यूशन प्राप्त कर सकते हैं, लेकिन अक्सर गति की कीमत पर ऐसा करते हैं। इस कारण से, ये कन्वर्टर्स ऑडियो या सिग्नल प्रोसेसिंग एप्लिकेशन में नहीं पाए जाते हैं। उनका उपयोग आम तौर पर डिजिटल वाल्टमीटर और अन्य उपकरणों तक सीमित होता है जिन्हें अत्यधिक सटीक माप की आवश्यकता होती है।

मूल डिजाइन: डुअल-स्लोप एडीसी

बुनियादी एकीकृत एडीसी सर्किट में एक इंटीग्रेटर होता है, मापने के लिए वोल्टेज और संदर्भ वोल्टेज के बीच चयन करने के लिए एक स्विच, एक टाइमर जो निर्धारित करता है कि अज्ञात को एकीकृत करने में कितना समय लगता है और मापता है कि संदर्भ एकीकरण कितना समय लगा, शून्य क्रॉसिंग का पता लगाने के लिए एक तुलनित्र , और एक नियंत्रक। कार्यान्वयन के आधार पर, इंटीग्रेटर को रीसेट करने की अनुमति देने के लिए इंटीग्रेटर कैपेसिटर के समानांतर एक स्विच भी मौजूद हो सकता है। नियंत्रक के इनपुट में एक घड़ी (समय को मापने के लिए उपयोग की जाती है) और एक तुलनित्र का आउटपुट शामिल होता है जिसका पता लगाने के लिए उपयोग किया जाता है जब इंटीग्रेटर का आउटपुट शून्य हो जाता है।

रूपांतरण दो चरणों में होता है: रन-अप चरण, जहां इंटीग्रेटर का इनपुट मापा जाने वाला वोल्टेज है, और रन-डाउन चरण, जहां इंटीग्रेटर का इनपुट एक ज्ञात संदर्भ वोल्टेज है। रन-अप चरण के दौरान, स्विच मापा वोल्टेज को इंटीग्रेटर के इनपुट के रूप में चुनता है। इंटीग्रेटर कैपेसिटर पर चार्ज बनाने की अनुमति देने के लिए इंटीग्रेटर को निश्चित अवधि के लिए रैंप करने की अनुमति है। रन-डाउन चरण के दौरान, स्विच संदर्भ वोल्टेज को इंटीग्रेटर के इनपुट के रूप में चुनता है। इंटीग्रेटर के आउटपुट को शून्य पर लौटने में लगने वाले समय को इस चरण के दौरान मापा जाता है।

इंटीग्रेटर वोल्टेज को कम करने के लिए संदर्भ वोल्टेज के लिए, संदर्भ वोल्टेज को इनपुट वोल्टेज के विपरीत एक ध्रुवीयता की आवश्यकता होती है। ज्यादातर मामलों में, सकारात्मक इनपुट वोल्टेज के लिए, इसका मतलब है कि संदर्भ वोल्टेज नकारात्मक होगा। सकारात्मक और नकारात्मक इनपुट वोल्टेज दोनों को संभालने के लिए, सकारात्मक और नकारात्मक संदर्भ वोल्टेज की आवश्यकता होती है। रन-डाउन चरण के दौरान उपयोग किए जाने वाले संदर्भ का चयन रन-अप चरण के अंत में इंटीग्रेटर आउटपुट की ध्रुवीयता पर आधारित होगा।

इंटीग्रेटर (एक स्थिर इनपुट मानते हुए) के आउटपुट के लिए मूल समीकरण है:

यह मानते हुए कि प्रत्येक रूपांतरण की शुरुआत में प्रारंभिक इंटीग्रेटर वोल्टेज शून्य है और रन डाउन अवधि के अंत में इंटीग्रेटर वोल्टेज शून्य होगा, हमारे पास निम्नलिखित दो समीकरण हैं जो रूपांतरण के दो चरणों के दौरान इंटीग्रेटर के आउटपुट को कवर करते हैं:

दो समीकरणों को जोड़ा और हल किया जा सकता है , अज्ञात इनपुट वोल्टेज:

समीकरण से, एडीसी को एकीकृत करने वाली दोहरी ढलान के लाभों में से एक स्पष्ट हो जाता है: माप सर्किट तत्वों (आर और सी) के मूल्यों से स्वतंत्र है। हालांकि, इसका मतलब यह नहीं है कि एडीसी को एकीकृत करने वाली दोहरी ढलान के डिजाइन में आर और सी के मूल्य महत्वहीन हैं (जैसा कि नीचे समझाया जाएगा)।

ध्यान दें कि ग्राफ़ में, वोल्टेज रन-अप चरण के दौरान ऊपर जा रहा है और रन-डाउन चरण के दौरान नीचे जा रहा है। वास्तव में, क्योंकि इंटीग्रेटर एक नकारात्मक प्रतिक्रिया कॉन्फ़िगरेशन में op-amp का उपयोग करता है, एक सकारात्मक लागू करता है इंटीग्रेटर के आउटपुट को नीचे जाने का कारण बनेगा। अप और डाउन अधिक सटीक रूप से रन-अप चरण के दौरान इंटीग्रेटर कैपेसिटर में चार्ज जोड़ने और रन-डाउन चरण के दौरान चार्ज हटाने की प्रक्रिया को संदर्भित करता है।

एडीसी को एकीकृत करने वाली दोहरी ढलान का संकल्प मुख्य रूप से रन-डाउन अवधि की लंबाई और समय माप संकल्प (यानी, नियंत्रक की घड़ी की आवृत्ति) द्वारा निर्धारित किया जाता है। आवश्यक रिज़ॉल्यूशन (बिट्स की संख्या में) पूर्ण-स्तरीय इनपुट के लिए रन-डाउन अवधि की न्यूनतम लंबाई निर्धारित करता है (उदा। ):

पूर्ण पैमाने पर इनपुट की माप के दौरान, इंटीग्रेटर के आउटपुट का ढलान रन-अप और रन-डाउन चरणों के दौरान समान होगा। इसका तात्पर्य यह भी है कि रन-अप अवधि और रन-डाउन अवधि का समय बराबर होगा () और कुल माप समय होगा . इसलिए, पूर्ण पैमाने पर इनपुट के लिए कुल माप समय वांछित संकल्प और नियंत्रक की घड़ी की आवृत्ति पर आधारित होगा:

आम तौर पर रन-अप समय को मुख्य आवृत्ति की अवधि के एक गुणक के रूप में चुना जाता है, मुख्य गुंजन को दबाने के लिए।

सीमाएं

एडीसी को एकीकृत करने वाले दोहरे ढलान के अधिकतम रिज़ॉल्यूशन की सीमाएँ हैं। लंबे माप समय या तेज घड़ियों का उपयोग करके बुनियादी दोहरे ढलान वाले एडीसी के संकल्प को मनमाने ढंग से उच्च मूल्यों तक बढ़ाना संभव नहीं है। संकल्प द्वारा सीमित है:

- एकीकृत एम्पलीफायर की सीमा। ऑप-एम्प पर वोल्टेज रेल इंटीग्रेटर के आउटपुट वोल्टेज को सीमित करता है। इंटीग्रेटर से बहुत लंबे समय तक जुड़ा एक इनपुट अंततः op amp को अपने आउटपुट को कुछ अधिकतम मान तक सीमित करने का कारण बनेगा, जिससे रन-डाउन समय के आधार पर कोई भी गणना अर्थहीन हो जाएगी। इसलिए इंटीग्रेटर के रेसिस्टर और कैपेसिटर को ऑप-एम्प के वोल्टेज रेल, रेफरेंस वोल्टेज और अपेक्षित फुल-स्केल इनपुट, और वांछित रिज़ॉल्यूशन को प्राप्त करने के लिए आवश्यक सबसे लंबे रन-अप समय के आधार पर सावधानी से चुना जाता है।

- अशक्त डिटेक्टर के रूप में उपयोग किए जाने वाले तुलनित्र की सटीकता। वाइडबैंड सर्किट शोर तुलनित्र की पहचान करने की क्षमता को सीमित करता है जब इंटीग्रेटर का आउटपुट शून्य तक पहुंच गया हो। गोएके सुझाव देते हैं कि एक विशिष्ट सीमा 1 मिलीवोल्ट का तुलनित्र रिज़ॉल्यूशन है।[1]

- इंटीग्रेटर के कैपेसिटर की गुणवत्ता। यद्यपि समाकलन करने वाले संधारित्र को पूरी तरह से रेखीय होने की आवश्यकता नहीं है, इसे समय-अपरिवर्तनीय होने की आवश्यकता है। ढांकता हुआ अवशोषण रैखिकता त्रुटियों का कारण बनता है।[2]

संवर्द्धन

एडीसी को एकीकृत करने वाले दोहरे ढलान के मूल डिजाइन में रैखिकता, रूपांतरण की गति और संकल्प की सीमाएं हैं। इन्हें कुछ हद तक दूर करने के लिए मूल डिजाइन में कई संशोधन किए गए हैं।

रन-अप सुधार

बढ़ाया दोहरी ढलान

बुनियादी दोहरी ढलान डिजाइन का रन-अप चरण एक निश्चित अवधि के लिए इनपुट वोल्टेज को एकीकृत करता है। यही है, यह इंटीग्रेटर के कैपेसिटर पर अज्ञात मात्रा में चार्ज करने की अनुमति देता है। अज्ञात वोल्टेज को निर्धारित करने के लिए इस अज्ञात चार्ज को मापने के लिए रन-डाउन चरण का उपयोग किया जाता है। संदर्भ वोल्टेज के बराबर पूर्ण पैमाने पर इनपुट के लिए, माप का आधा समय रन-अप चरण में व्यतीत होता है। रन-अप चरण में बिताए गए समय को कम करने से कुल माप समय कम हो सकता है। एक सामान्य कार्यान्वयन संदर्भ वोल्टेज के रूप में दो बार बड़ी इनपुट श्रेणी का उपयोग करता है।

रन-अप समय को कम करने का एक आसान तरीका इनपुट पर उपयोग किए जाने वाले प्रतिरोधी के आकार को कम करके इंटीग्रेटर कैपेसिटर पर जमा होने वाले चार्ज को बढ़ाना है। यह अभी भी समान कुल मात्रा में चार्ज संचय की अनुमति देता है, लेकिन यह ऐसा कम समय में करता है। अज्ञात इनपुट वोल्टेज की गणना के लिए निम्न समीकरण में रन-डाउन चरण के परिणामों के लिए समान एल्गोरिदम का उपयोग करना ():

ध्यान दें कि यह समीकरण, बुनियादी दोहरे ढलान वाले कनवर्टर के समीकरण के विपरीत, इंटीग्रेटर प्रतिरोधों के मूल्यों पर निर्भर करता है। या इससे भी महत्वपूर्ण बात यह है कि यह दो प्रतिरोध मानों के अनुपात पर निर्भर करता है। यह संशोधन कनवर्टर के रिज़ॉल्यूशन में सुधार करने के लिए कुछ नहीं करता है (चूंकि यह ऊपर उल्लिखित रिज़ॉल्यूशन सीमाओं में से किसी को भी संबोधित नहीं करता है)।

बहु-ढलान रन-अप

रन-अप चरण का उद्देश्य इंटीग्रेटर में इनपुट वोल्टेज के आनुपातिक चार्ज को बाद में रन-डाउन चरण के दौरान मापा जाना है। कनवर्टर के रिज़ॉल्यूशन में सुधार करने का एक तरीका रन-अप चरण के दौरान एकीकृत एम्पलीफायर की सीमा को कृत्रिम रूप से बढ़ाना है।

इंटीग्रेटर क्षमता को बढ़ाने का एक तरीका रन-अप चरण के दौरान समय-समय पर चार्ज की ज्ञात मात्रा को जोड़ना या घटाना है ताकि इंटीग्रेटर के आउटपुट को इंटीग्रेटर एम्पलीफायर की सीमा के भीतर रखा जा सके। कुल संचित चार्ज अज्ञात इनपुट वोल्टेज द्वारा पेश किया गया चार्ज है और ज्ञात शुल्कों का योग जो जोड़ा या घटाया गया था।

दाईं ओर दिखाया गया सर्किट डायग्राम इस बात का उदाहरण है कि मल्टी-स्लोप रन-अप को कैसे लागू किया जा सकता है। रन-अप के दौरान अज्ञात इनपुट वोल्टेज, , हमेशा इंटीग्रेटर पर लागू होता है। दो स्वतंत्र स्विचों द्वारा नियंत्रित सकारात्मक और नकारात्मक संदर्भ वोल्टेज, इंटीग्रेटर के आउटपुट को उसकी सीमा के भीतर रखने के लिए आवश्यकतानुसार चार्ज जोड़ते और घटाते हैं। संदर्भ प्रतिरोधक, और से छोटे होते हैं यह सुनिश्चित करने के लिए कि संदर्भ इनपुट द्वारा लगाए गए शुल्क को दूर कर सकते हैं। इंटीग्रेटर के आउटपुट से जुड़े एक तुलनित्र का उपयोग यह तय करने के लिए किया जाता है कि किस संदर्भ वोल्टेज को लागू किया जाना चाहिए। यह एक अपेक्षाकृत सरल एल्गोरिद्म हो सकता है: यदि इंटीग्रेटर का आउटपुट दहलीज से ऊपर है, तो सकारात्मक संदर्भ को सक्षम करें (आउटपुट को नीचे जाने का कारण); यदि इंटीग्रेटर का आउटपुट थ्रेशोल्ड से नीचे है, तो नकारात्मक संदर्भ को सक्षम करें (आउटपुट को ऊपर जाने के लिए)। संदर्भ वोल्टेज के परिणामस्वरूप इंटीग्रेटर कैपेसिटर पर लगाए गए (या हटाए गए) अतिरिक्त चार्ज के लिए नियंत्रक कितनी बार चालू होता है, इस पर नज़र रखता है। मल्टी-स्लोप रन-अप के दौरान जोड़ा/घटाया गया चार्ज परिणाम का मोटा हिस्सा होता है (उदाहरण के लिए अग्रणी 3 अंक)।

दाईं ओर ऐसे मल्टी-स्लोप रन-अप के दौरान इंटीग्रेटर से सैंपल आउटपुट का एक ग्राफ है। प्रत्येक धराशायी ऊर्ध्वाधर रेखा नियंत्रक द्वारा एक निर्णय बिंदु का प्रतिनिधित्व करती है जहां यह आउटपुट की ध्रुवीयता का नमूना लेती है और इनपुट के लिए सकारात्मक या नकारात्मक संदर्भ वोल्टेज को लागू करने का विकल्प चुनती है। आदर्श रूप से, रन-अप अवधि के अंत में इंटीग्रेटर के आउटपुट वोल्टेज को निम्नलिखित समीकरण द्वारा दर्शाया जा सकता है:

कहाँ नमूना अवधि है, उन अवधियों की संख्या है जिनमें सकारात्मक संदर्भ स्विच किया गया है, उन अवधियों की संख्या है जिनमें नकारात्मक संदर्भ स्विच किया गया है, और रन-अप चरण में अवधियों की कुल संख्या है।

रन-अप के दौरान प्राप्त संकल्प रन-अप एल्गोरिथम की अवधियों की संख्या द्वारा दिया जाता है। मल्टी-स्लो रन-अप के कई फायदे हैं:

- जैसा कि एनालॉग संग्रहित चार्ज बहुत छोटा है, इंटीग्रेशन कैपेसिटर छोटा हो सकता है और इस प्रकार एक ही चार्ज के लिए इंटीग्रेटर आउटपुट पर एक उच्च वोल्टेज मौजूद होता है। यह तुलनित्र शोर को कम महत्वपूर्ण बनाता है और छोटे शुल्कों को हल किया जा सकता है।

- कैपेसिटर में कम चार्ज जमा होने से डाइइलेक्ट्रिक अवशोषण का प्रभाव कम होता है। यह दोहरी ढलान एडीसी के लिए रैखिकता त्रुटि का एक प्रमुख स्रोत कम करता है।

- कम चार्ज में रन-डाउन काफी तेज हो सकता है। परिणाम का एक हिस्सा रन-अप के दौरान पहले ही प्राप्त हो चुका है।

- रन-अप एल्गोरिथम में चक्रों की संख्या को बदलकर, रन-अप चरण की लंबाई बिना किसी समस्या के भिन्न हो सकती है। तो उसी हार्डवेयर का उपयोग कम रिज़ॉल्यूशन वाले तेज़ रूपांतरण या उच्च रिज़ॉल्यूशन वाले धीमे रूपांतरण के लिए किया जा सकता है। दोहरी ढलान एडीसी कम लचीला है, आदर्श रूप से इंटीग्रेटर के आउटपुट स्विंग का पूर्ण उपयोग करने के लिए एकीकरण समय के अनुपात में एक एकीकरण संधारित्र।

जबकि मल्टी-स्लोप रन-अप को अनिश्चित काल तक जारी रखना संभव है, केवल लंबे रन-अप समय का उपयोग करके कनवर्टर के रिज़ॉल्यूशन को मनमाने ढंग से उच्च स्तर तक बढ़ाना संभव नहीं है। संदर्भों को नियंत्रित करने वाले स्विच की कार्रवाई, स्विच के बीच क्रॉस-कपलिंग, अनपेक्षित स्विच चार्ज इंजेक्शन, संदर्भों में बेमेल और समय की त्रुटियों के माध्यम से त्रुटि को मल्टी-स्लोप रन-अप में पेश किया जाता है।[3] स्विच के सावधानीपूर्वक संचालन से इस त्रुटि में से कुछ को कम किया जा सकता है।[4][5] विशेष रूप से, रन-अप अवधि के दौरान, प्रत्येक स्विच को लगातार कई बार सक्रिय किया जाना चाहिए। ऊपर समझाया गया एल्गोरिथ्म ऐसा नहीं करता है और केवल इंटीग्रेटर आउटपुट को सीमा के भीतर रखने के लिए आवश्यकतानुसार स्विच को टॉगल करता है। प्रत्येक स्विच को लगातार कई बार सक्रिय करने से स्विचिंग से संबंधित त्रुटि लगभग स्थिर हो जाती है। कोई भी आउटपुट ऑफ़सेट जो स्विचिंग त्रुटि का परिणाम है, को मापा जा सकता है और फिर परिणाम से संख्यात्मक रूप से घटाया जा सकता है।

रन-डाउन सुधार

बहु-ढलान रन-डाउन

सरल, सिंगल-स्लोप रन-डाउन धीमा है। आमतौर पर, रन डाउन टाइम को क्लॉक टिक में मापा जाता है, इसलिए चार अंकों का रिज़ॉल्यूशन प्राप्त करने के लिए, रनडाउन टाइम में 10,000 क्लॉक साइकिल तक का समय लग सकता है। एक बहु-ढलान रन-डाउन सटीकता का त्याग किए बिना माप को गति दे सकता है। 4 ढलान दरों का उपयोग करके, जो पिछले की तुलना में दस अधिक क्रमिक शक्ति हैं, चार अंकों का रिज़ॉल्यूशन लगभग 40 क्लॉक टिक में प्राप्त किया जा सकता है - एक विशाल गति सुधार।[6]

दाईं ओर दिखाया गया सर्किट बहु-ढलान रन-डाउन सर्किट का एक उदाहरण है जिसमें चार रन-डाउन ढलान हैं, जिनमें से प्रत्येक पिछले की तुलना में दस गुना अधिक क्रमिक है। स्विच नियंत्रित करते हैं कि कौन सा ढलान चुना गया है। युक्त स्विच सबसे तेज ढलान का चयन करता है (यानी, इंटीग्रेटर आउटपुट को सबसे तेजी से शून्य की ओर बढ़ने का कारण बनेगा)। रन-डाउन अंतराल की शुरुआत में, सर्किट से जुड़े स्विच को खोलकर अज्ञात इनपुट को हटा दिया जाता है और बंद कर रहा है बदलना। एक बार जब इंटीग्रेटर का आउटपुट शून्य (और रन-डाउन समय मापा जाता है) तक पहुंच जाता है, तो स्विच को खोला जाता है और बंद करके अगला स्लोप चुना जाता है बदलना। यह अंतिम ढलान तक दोहराता है शून्य पर पहुंच गया है। प्रत्येक ढलान के लिए रन-डाउन समय का संयोजन अज्ञात इनपुट का मान निर्धारित करता है। संक्षेप में, प्रत्येक ढलान परिणाम में संकल्प का एक अंक जोड़ता है।

मल्टी-स्लोप रन-डाउन का उपयोग अक्सर मल्टी-स्लोप रन-अप के संयोजन में किया जाता है। मल्टी-स्लोप रन-अप इंटीग्रेटर पर एक अपेक्षाकृत छोटे कैपेसिटर के लिए अनुमति देता है और इस प्रकार एक अपेक्षाकृत खड़ी ढलान के साथ शुरू होता है और इस प्रकार वास्तव में बहुत अधिक क्रमिक ढलानों का उपयोग करने का विकल्प होता है। एक साधारण रन-अप (जैसे दोहरी-ढलान एडीसी) के साथ एक बहु-ढलान रंडाउन का उपयोग करना संभव है, लेकिन प्रारंभिक चरण के लिए पहले से ही अपेक्षाकृत छोटी ढलान से सीमित है और बहुत छोटी ढलानों के लिए ज्यादा जगह नहीं है।

उदाहरण सर्किट में, स्लोप रेसिस्टर्स 10 के गुणक से भिन्न होते हैं। यह मान, आधार के रूप में जाना जाता है (), कोई भी मूल्य हो सकता है। जैसा कि नीचे समझाया गया है, आधार की पसंद कनवर्टर की गति को प्रभावित करती है और वांछित संकल्प प्राप्त करने के लिए आवश्यक ढलानों की संख्या निर्धारित करती है।

इस डिजाइन का आधार यह धारणा है कि रन-डाउन अंतराल के अंत में शून्य क्रॉसिंग खोजने का प्रयास करते समय हमेशा ओवरशूट होगा। कनवर्टर की घड़ी के आधार पर तुलनित्र के आवधिक नमूने के कारण यह सही होगा। अगर हम मानते हैं कि कनवर्टर एक घड़ी चक्र में एक ढलान से दूसरे पर स्विच करता है (जो संभव हो सकता है या नहीं भी हो सकता है), किसी दिए गए ढलान के लिए ओवरशूट की अधिकतम मात्रा एक घड़ी अवधि में सबसे बड़ा इंटीग्रेटर आउटपुट परिवर्तन होगा:

इस ओवरशूट को दूर करने के लिए, अगले ढलान को इससे अधिक की आवश्यकता नहीं होगी घड़ी चक्र, जो रन-डाउन के कुल समय पर एक बाउंड लगाने में मदद करता है। प्रथम-रन डाउन (सबसे तेज ढलान का उपयोग करके) का समय अज्ञात इनपुट पर निर्भर है (यानी, रन-अप चरण के दौरान इंटीग्रेटर कैपेसिटर पर लगाए गए चार्ज की मात्रा)। अधिक से अधिक, यह होगा:

कहाँ पहली ढलान के लिए घड़ी की अवधि की अधिकतम संख्या है, रन-डाउन चरण की शुरुआत में अधिकतम इंटीग्रेटर वोल्टेज है, और पहले ढलान के लिए इस्तेमाल किया जाने वाला प्रतिरोधक है।

चयनित आधार के आधार पर शेष ढलानों की सीमित अवधि होती है, इसलिए रूपांतरण का शेष समय (कनवर्टर घड़ी अवधि में) है:

कहाँ ढलानों की संख्या है।

बहु-ढलान रन-डाउन के दौरान मापा समय अंतराल को मापा वोल्टेज में परिवर्तित करना बहु-ढलान रन-अप वृद्धि में उपयोग की जाने वाली चार्ज-बैलेंसिंग विधि के समान है। प्रत्येक ढलान इंटीग्रेटर कैपेसिटर से/से चार्ज की ज्ञात मात्रा को जोड़ता या घटाता है। रन-अप ने समाकलक में कुछ अज्ञात मात्रा में आवेश जोड़ा होगा। फिर, रन-डाउन के दौरान, पहली ढलान बड़ी मात्रा में चार्ज घटाती है, दूसरी ढलान चार्ज की एक छोटी राशि जोड़ती है, आदि प्रत्येक बाद की ढलान लक्ष्य के साथ पिछले ढलान की विपरीत दिशा में एक छोटी राशि चलती है। शून्य के और करीब पहुंचना। प्रत्येक ढलान आवेश की मात्रा जोड़ता या घटाता है ढलान के प्रतिरोधक और ढलान की अवधि के समानुपाती:

आवश्यक रूप से एक पूर्णांक है और आदर्श रूप से इससे कम या इसके बराबर होगा दूसरे और बाद के ढलानों के लिए। उदाहरण के तौर पर उपरोक्त सर्किट का उपयोग करते हुए, दूसरी ढलान, , निम्न शुल्क योगदान कर सकते हैं, , इंटीग्रेटर के लिए:

- के चरणों में

वह है, पहले ढलान के सबसे छोटे चरण के बराबर सबसे बड़े संभावित मान, या प्रति ढलान के रिज़ॉल्यूशन का एक (आधार 10) अंक। इसे सामान्य करते हुए, हम ढलानों की संख्या का प्रतिनिधित्व कर सकते हैं, , आधार और आवश्यक संकल्प के संदर्भ में, :

इसे वापस दूसरे और बाद के ढलानों के लिए आवश्यक रन-डाउन समय का प्रतिनिधित्व करने वाले समीकरण में प्रतिस्थापित करना हमें यह देता है:

जिसका मूल्यांकन करने पर पता चलता है कि ई (गणितीय स्थिरांक) के आधार का उपयोग करके न्यूनतम रन-डाउन समय प्राप्त किया जा सकता है। परिणाम की गणना में जटिलता और उपयुक्त प्रतिरोधी नेटवर्क खोजने के मामले में इस आधार का उपयोग करना मुश्किल हो सकता है, इसलिए 2 या 4 का आधार अधिक सामान्य होगा।

अवशेष एडीसी

मल्टी-स्लोप रन-अप जैसे रन-अप एन्हांसमेंट का उपयोग करते समय, जहां रन-अप चरण के दौरान कनवर्टर के रिज़ॉल्यूशन का एक हिस्सा हल हो जाता है, दूसरे प्रकार के एनालॉग का उपयोग करके रन-डाउन चरण को पूरी तरह से समाप्त करना संभव है- टू-डिजिटल कनवर्टर।[7] एक बहु-ढलान रन-अप रूपांतरण के रन-अप चरण के अंत में, इंटीग्रेटर के कैपेसिटर पर अभी भी अज्ञात मात्रा में चार्ज शेष रहेगा। इस अज्ञात चार्ज को निर्धारित करने के लिए एक पारंपरिक रन-डाउन चरण का उपयोग करने के बजाय, अज्ञात वोल्टेज को दूसरे कनवर्टर द्वारा सीधे परिवर्तित किया जा सकता है और अज्ञात इनपुट वोल्टेज को निर्धारित करने के लिए रन-अप चरण के परिणाम के साथ जोड़ा जा सकता है।

यह मानते हुए कि ऊपर वर्णित बहु-ढलान रन-अप का उपयोग किया जा रहा है, अज्ञात इनपुट वोल्टेज बहु-ढलान रन-अप काउंटर से संबंधित हो सकता है, और , और मापा गया इंटीग्रेटर आउटपुट वोल्टेज, निम्नलिखित समीकरण का उपयोग करना (बहु-ढलान रन-अप आउटपुट समीकरण से प्राप्त):

यह समीकरण आदर्श घटकों को मानते हुए इनपुट वोल्टेज की सैद्धांतिक गणना का प्रतिनिधित्व करता है। चूंकि समीकरण लगभग सभी सर्किट के पैरामीटर पर निर्भर करता है, संदर्भ धाराओं में कोई भिन्नता, इंटीग्रेटर कैपेसिटर, या अन्य मान परिणाम में त्रुटियों का परिचय देंगे। एक अंशांकन कारक आमतौर पर इसमें शामिल होता है मापा त्रुटियों के लिए खाते में शब्द (या, जैसा कि संदर्भित पेटेंट में वर्णित है, अवशिष्ट एडीसी के आउटपुट को रन-अप काउंटरों की इकाइयों में परिवर्तित करने के लिए)।

रन-डाउन चरण को पूरी तरह से समाप्त करने के लिए उपयोग किए जाने के बजाय, अवशेष एडीसी का उपयोग रन-डाउन चरण को अन्यथा संभव होने की तुलना में अधिक सटीक बनाने के लिए भी किया जा सकता है।[8] पारंपरिक रन-डाउन चरण के साथ, रन-डाउन समय माप अवधि शून्य वोल्ट के माध्यम से इंटीग्रेटर आउटपुट क्रॉसिंग के साथ समाप्त होती है। एक तुलनित्र का उपयोग करके शून्य क्रॉसिंग का पता लगाने में एक निश्चित मात्रा में त्रुटि शामिल है (जैसा कि ऊपर बताया गया है कि मूल दोहरे-ढलान डिजाइन की कमियों में से एक)। इंटीग्रेटर आउटपुट (उदाहरण के लिए कनवर्टर नियंत्रक की घड़ी के साथ सिंक्रनाइज़) को तेजी से नमूना करने के लिए अवशेष एडीसी का उपयोग करके, वोल्टेज रीडिंग को शून्य क्रॉसिंग के तुरंत पहले और तुरंत बाद में लिया जा सकता है (जैसा कि एक तुलनित्र के साथ मापा जाता है)। रन-डाउन चरण के दौरान इंटीग्रेटर वोल्टेज की ढलान स्थिर होने के कारण, दो वोल्टेज मापों को इंटरपोलेशन फ़ंक्शन के इनपुट के रूप में उपयोग किया जा सकता है जो शून्य-क्रॉसिंग के समय को अधिक सटीक रूप से निर्धारित करता है (यानी, बहुत अधिक रिज़ॉल्यूशन के साथ) नियंत्रक की घड़ी अकेले अनुमति देगी)।

अन्य सुधार

निरंतर-एकीकृत कनवर्टर

इन संवर्द्धन में से कुछ को बुनियादी दोहरे-ढलान डिजाइन (अर्थात् बहु-ढलान रन-अप और अवशेष एडीसी) के संयोजन से, एक एकीकृत एनालॉग-टू-डिजिटल कनवर्टर का निर्माण संभव है जो बिना किसी आवश्यकता के लगातार संचालन करने में सक्षम है एक रन-डाउन अंतराल।[9] वैचारिक रूप से, मल्टी-स्लोप रन-अप एल्गोरिथम को लगातार काम करने की अनुमति है। रूपांतरण शुरू करने के लिए, दो चीजें एक साथ होती हैं: अवशेष एडीसी का उपयोग वर्तमान में इंटीग्रेटर कैपेसिटर पर अनुमानित चार्ज को मापने के लिए किया जाता है और मल्टी-स्लोप रन-अप की निगरानी करने वाले काउंटरों को रीसेट कर दिया जाता है। रूपांतरण अवधि के अंत में, एक और अवशेष एडीसी रीडिंग ली जाती है और मल्टी-स्लोप रन-अप काउंटरों के मूल्यों को नोट किया जाता है।

अज्ञात इनपुट की गणना अवशेष एडीसी के लिए उपयोग किए गए समान समीकरण का उपयोग करके की जाती है, सिवाय इसके कि दो आउटपुट वोल्टेज शामिल हैं ( रूपांतरण की शुरुआत में मापा इंटीग्रेटर वोल्टेज का प्रतिनिधित्व करना, और रूपांतरण के अंत में मापा इंटीग्रेटर वोल्टेज का प्रतिनिधित्व करना।

ऐसा निरंतर-एकीकृत कनवर्टर डेल्टा-सिग्मा मॉड्यूलेशन | डेल्टा-सिग्मा एनालॉग-टू-डिजिटल कनवर्टर के समान है।

अंशांकन

दोहरी-ढलान एकीकृत कनवर्टर के अधिकांश रूपों में, कनवर्टर का प्रदर्शन एक या अधिक सर्किट पैरामीटर पर निर्भर होता है। बुनियादी डिजाइन के मामले में, कनवर्टर का आउटपुट संदर्भ वोल्टेज के संदर्भ में होता है। अधिक उन्नत डिजाइनों में, सर्किट में उपयोग किए जाने वाले एक या अधिक प्रतिरोधों पर या उपयोग किए जा रहे इंटीग्रेटर कैपेसिटर पर भी निर्भरता होती है। सभी मामलों में, महंगे सटीक घटकों का उपयोग करने पर भी ऐसे अन्य प्रभाव हो सकते हैं जिनका सामान्य दोहरे-ढलान समीकरणों (संधारित्र पर ढांकता हुआ प्रभाव या किसी भी घटक पर आवृत्ति या तापमान निर्भरता) के लिए जिम्मेदार नहीं है। इनमें से किसी भी भिन्नता के परिणामस्वरूप कनवर्टर के आउटपुट में त्रुटि होती है। सबसे अच्छे मामले में, यह केवल लाभ और/या ऑफसेट त्रुटि है। सबसे खराब स्थिति में, गैर-रैखिकता या गैर-एकरूपता का परिणाम हो सकता है।

कुछ अंशांकन कनवर्टर के लिए आंतरिक रूप से किया जा सकता है (यानी, किसी विशेष बाहरी इनपुट की आवश्यकता नहीं है)। इस प्रकार का अंशांकन हर बार कनवर्टर चालू होने पर, समय-समय पर कनवर्टर चल रहा है, या केवल जब एक विशेष अंशांकन मोड दर्ज किया जाता है। एक अन्य प्रकार के अंशांकन के लिए ज्ञात मात्रा के बाहरी इनपुट की आवश्यकता होती है (उदाहरण के लिए, वोल्टेज संदर्भ या सटीक प्रतिरोध संदर्भ) और आम तौर पर कभी-कभी किया जाता है (हर साल सामान्य परिस्थितियों में उपयोग किए जाने वाले उपकरणों के लिए, अधिकतर जब मैट्रोलोजी अनुप्रयोगों में उपयोग किया जाता है)।

इन प्रकार की त्रुटियों में से, ऑफसेट त्रुटि को ठीक करना सबसे सरल है (यह मानते हुए कि कनवर्टर की पूरी रेंज में एक स्थिर ऑफसेट है)। यह अक्सर समय-समय पर ग्राउंड पोटेंशियल का माप लेकर कन्वर्टर के अंदर ही किया जाता है। आदर्श रूप से, जमीन को मापने का परिणाम हमेशा शून्य आउटपुट होना चाहिए। कोई गैर-शून्य आउटपुट कनवर्टर में ऑफ़सेट त्रुटि इंगित करता है। यही है, अगर जमीन की माप के परिणामस्वरूप 0.001 वोल्ट का उत्पादन होता है, तो कोई यह मान सकता है कि सभी माप समान मात्रा से ऑफसेट हो जाएंगे और बाद के सभी परिणामों से 0.001 घटा सकते हैं।

लाभ त्रुटि को इसी तरह मापा जा सकता है और आंतरिक रूप से ठीक किया जा सकता है (फिर से यह मानते हुए कि संपूर्ण आउटपुट रेंज पर निरंतर लाभ त्रुटि है)। वोल्टेज संदर्भ (या सीधे संदर्भ से प्राप्त कुछ वोल्टेज) को कनवर्टर के इनपुट के रूप में इस्तेमाल किया जा सकता है। यदि धारणा यह है कि वोल्टेज संदर्भ सटीक है (कनवर्टर की सहनशीलता के भीतर) या वोल्टेज संदर्भ को वोल्टेज मानक के खिलाफ बाह्य रूप से कैलिब्रेट किया गया है, माप में कोई त्रुटि कनवर्टर में लाभ त्रुटि होगी। यदि, उदाहरण के लिए, एक कनवर्टर के 5 वोल्ट संदर्भ के मापन के परिणामस्वरूप 5.3 वोल्ट का उत्पादन होता है (किसी ऑफसेट त्रुटि के लिए लेखांकन के बाद), 0.94 (5 / 5.3) का लाभ गुणक किसी भी बाद के माप परिणामों पर लागू किया जा सकता है।

यह भी देखें

- एनॉलॉग से डिजिटल परिवर्तित करने वाला उपकरण

- वाल्टमीटर

फुटनोट्स

- ↑ Goeke 1989, p. 9

- ↑ Hewlett-Packard Catalog, 1981, page 49, stating, "For small inputs, noise becomes a problem and for large inputs, the dielectric absorption of the capacitor becomes a problem."

- ↑ Eng & Matson 1994

- ↑ Eng & Matson 1994

- ↑ Goeke 1989

- ↑ Goeke 1989, p. 9, stating, "Multislope rundown reduces the time to perform rundown."

- ↑ Riedel 1992

- ↑ Regier 2001

- ↑ Goeke 1992

संदर्भ

- US 5321403, Eng, Benjamin, Jr. & Matson, Don, "Multiple Slope Analog-to-Digital Converter", issued 14 June 1994

- Goeke, Wayne (April 1989), "8.5-Digit Integrating Analog-to-Digital Converter with 16-Bit, 100,000-Sample-per-Second Performance" (PDF), HP Journal, 40 (2): 8–15

- US 5117227, Goeke, Wayne, "Continuously-integrating high-resolution analog-to-digital converter", issued 26 May 1992

- Kester, Walt (2005), The Data Conversion Handbook, ISBN 0-7506-7841-0

- US 6243034, Regier, Christopher, "Integrating analog to digital converter with improved resolution", issued 5 June 2001

- US 5101206, Riedel, Ronald, "Integrating analog to digital converter", issued 31 March 1992