ध्रुव विभाजन

ध्रुव विभाजन एक ऐसी घटना है जिसका उपयोग इलेक्ट्रॉनिक एम्पलीफायर में उपयोग की जाने वाली आवृत्ति क्षतिपूर्ति के कुछ रूपों में किया जाता है। जब ध्रुव (जटिल विश्लेषण) को आवृत्ति में सबसे कम (आमतौर पर एक इनपुट ध्रुव) को कम आवृत्तियों पर ले जाने के इरादे से एम्पलीफायर के इनपुट और आउटपुट पक्षों के बीच एक संधारित्र पेश किया जाता है, तो ध्रुव विभाजन आवृत्ति में अगले ध्रुव (आमतौर पर एक आउटपुट) का कारण बनता है ध्रुव) उच्च आवृत्ति पर जाने के लिए। यह ध्रुव संचलन एम्पलीफायर की स्थिरता को बढ़ाता है और कम गति की कीमत पर इसकी चरण प्रतिक्रिया में सुधार करता है।[1][2][3][4]

ध्रुव विभाजन का उदाहरण

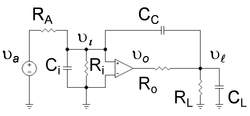

यह उदाहरण दिखाता है कि संधारित्र का परिचय सी के रूप में जाना जाता हैC चित्र 1 के एम्पलीफायर में दो परिणाम होते हैं: पहला, यह एम्पलीफायर के सबसे कम आवृत्ति वाले ध्रुव को आवृत्ति में और भी कम स्थानांतरित करने का कारण बनता है और दूसरा, यह उच्च ध्रुव को आवृत्ति में उच्चतर स्थानांतरित करने का कारण बनता है।[5] चित्र 1 के एम्पलीफायर में अतिरिक्त इनपुट प्रतिरोध आर के कारण कम आवृत्ति वाला पोल हैiऔर धारिता Ci, समय स्थिरांक C के साथi( आरA || आरi). यह ध्रुव मिलर के प्रमेय द्वारा आवृत्ति में नीचे की ओर खिसकता है। लोड प्रतिरोध आर को जोड़कर एम्पलीफायर को एक उच्च आवृत्ति आउटपुट पोल दिया जाता हैLऔर धारिता CL, समय स्थिरांक C के साथL( आरo || आरL). उच्च-आवृत्ति ध्रुव की ऊपर की ओर गति इसलिए होती है क्योंकि मिलर-प्रवर्धित मुआवजा संधारित्र सीCआउटपुट वोल्टेज डिवाइडर की आवृत्ति निर्भरता को बदल देता है।

पहला उद्देश्य, सबसे निचले ध्रुव को आवृत्ति में नीचे की ओर ले जाना दिखाना, मिलर प्रभाव|मिलर के प्रमेय लेख के समान दृष्टिकोण का उपयोग करके स्थापित किया गया है। मिलर के प्रमेय पर लेख में वर्णित प्रक्रिया के बाद, चित्र 1 का सर्किट चित्र 2 में बदल जाता है, जो विद्युत रूप से चित्र 1 के बराबर है। चित्र 2 के इनपुट पक्ष में किरचॉफ के वर्तमान कानून का अनुप्रयोग इनपुट वोल्टेज निर्धारित करता है लागू सिग्नल वोल्टेज के एक फ़ंक्शन के रूप में आदर्श ऑप amp के लिए , अर्थात्,

जो f से शुरू होने वाली आवृत्ति के साथ धड़ल्ले से बोलना प्रदर्शित करता है1कहाँ

जो संकेतन का परिचय देता है सबसे निचले ध्रुव के समय स्थिरांक के लिए। यह आवृत्ति एम्पलीफायर की प्रारंभिक कम आवृत्ति से कम है, जो सी के लिए हैC= 0 एफ है .

दूसरे उद्देश्य की ओर मुड़ते हुए, उच्च ध्रुव की चाल को आवृत्ति में और भी अधिक दिखाते हुए, सर्किट के आउटपुट पक्ष को देखना आवश्यक है, जो समग्र लाभ और अतिरिक्त आवृत्ति निर्भरता में एक दूसरे कारक का योगदान देता है। वोल्टेज एम्पलीफायर के अंदर आदर्श ऑप amp के लाभ से निर्धारित होता है

इस संबंध का उपयोग करना और सर्किट के आउटपुट पक्ष पर किरचॉफ के वर्तमान कानून को लागू करना लोड वोल्टेज निर्धारित करता है वोल्टेज के एक कार्य के रूप में आदर्श ऑप amp के इनपुट पर:

समग्र लाभ प्राप्त करने के लिए इस अभिव्यक्ति को सर्किट के इनपुट पक्ष के लिए पहले पाए गए लाभ कारक के साथ जोड़ा जाता है

यह लाभ सूत्र दो समय स्थिरांक के साथ एक सरल दो-ध्रुव प्रतिक्रिया दिखाता प्रतीत होता है। (यह अंश में एक शून्य भी प्रदर्शित करता है लेकिन, एम्पलीफायर लाभ ए मानते हुएvबड़ा है, यह शून्य केवल इस चर्चा में मायने रखने के लिए बहुत अधिक आवृत्तियों पर महत्वपूर्ण है, इसलिए अंश को एकता के रूप में अनुमानित किया जा सकता है।) हालांकि, एम्पलीफायर में दो-ध्रुव व्यवहार होता है, दो समय-स्थिरांक अधिक जटिल होते हैं उपरोक्त अभिव्यक्ति से पता चलता है क्योंकि मिलर कैपेसिटेंस में एक छिपी हुई आवृत्ति निर्भरता होती है जिसका कम आवृत्तियों पर कोई महत्व नहीं है, लेकिन उच्च आवृत्तियों पर इसका काफी प्रभाव पड़ता है। अर्थात्, आउटपुट आर-सी उत्पाद, सी मानते हुएL( आरo || आरL), कम आवृत्ति ध्रुव के काफी ऊपर की आवृत्ति से मेल खाता है, मिलर के प्रमेय के बजाय मिलर कैपेसिटेंस के सटीक रूप का उपयोग किया जाना चाहिए। मिलर के प्रमेय पर लेख के अनुसार, मिलर कैपेसिटेंस द्वारा दिया जाता है

(सकारात्मक मिलर धारिता के लिए, एvनकारात्मक है।) इस परिणाम को लाभ अभिव्यक्ति और संग्रह शर्तों में प्रतिस्थापित करने पर, लाभ को इस प्रकार फिर से लिखा जाता है:

डी के साथωω में एक द्विघात द्वारा दिया गया, अर्थात्:

प्रत्येक द्विघात के दो गुणनखंड होते हैं, और यदि इसे इस रूप में दोबारा लिखा जाए तो यह अभिव्यक्ति सरल लगती है

कहाँ और डी के सूत्र में कैपेसिटेंस और प्रतिरोधों का संयोजन हैω.[6] वे एम्पलीफायर के दो ध्रुवों के समय स्थिरांक के अनुरूप हैं। एक या दूसरा समय स्थिरांक सबसे लंबा होता है; कल्पना करना निम्नतम ध्रुव के अनुरूप सबसे लंबा समय स्थिरांक है, और मान लीजिए >> . (अच्छे कदम की प्रतिक्रिया की आवश्यकता है >> . ध्रुव विभाजन#CC का चयन|C का चयन देखेंCनीचे।)

इस एम्पलीफायर के सबसे निचले ध्रुव के पास कम आवृत्तियों पर, आमतौर पर ω में रैखिक शब्द द्विघात शब्द से अधिक महत्वपूर्ण है, इसलिए डी का कम आवृत्ति व्यवहारωहै:

अब कहां सीMमिलर प्रभाव का उपयोग करके पुनः परिभाषित किया गया है

जो कि कम आवृत्तियों पर मूल्यांकित पिछली मिलर कैपेसिटेंस है। इस आधार पर निर्धारित किया जाता है, प्रदान किया जाता है >> . क्योंकि सीMबड़ा है, समय स्थिर है C के मूल मान से बहुत बड़ा हैi( आरA || आरi).[7] उच्च आवृत्तियों पर द्विघात पद महत्वपूर्ण हो जाता है। उपरोक्त परिणाम को मानते हुए मान्य है, दूसरी बार स्थिरांक, उच्च आवृत्ति ध्रुव की स्थिति, डी में द्विघात पद से पाई जाती हैωजैसा

इस अभिव्यक्ति में उत्पाद के अनुरूप द्विघात गुणांक को प्रतिस्थापित करना के लिए अनुमान के साथ , दूसरे ध्रुव की स्थिति का अनुमान मिलता है:

और क्योंकि सीMबड़ा है, ऐसा लगता है इसका आकार इसके मूल मान C से कम हो गया हैL( आरo|| आरL); अर्थात्, C के कारण ऊँचा ध्रुव आवृत्ति में और भी अधिक ऊपर चला गया हैC.[8] संक्षेप में, संधारित्र सी का परिचयCनिचले ध्रुव को नीचे और ऊंचे ध्रुव को ऊंचे स्थान पर ले जाया गया, इसलिए 'ध्रुव विभाजन' शब्द एक अच्छा विवरण प्रतीत होता है।

सी का चयनC

C के लिए कौन सा मूल्य अच्छा विकल्प है?C? सामान्य प्रयोजन के उपयोग के लिए, पारंपरिक डिज़ाइन (जिसे अक्सर डोमिनेंट-पोल या सिंगल-पोल कंपंसेशन कहा जाता है) के लिए एम्पलीफायर लाभ को कोने की आवृत्ति से 20 डीबी/दशक तक घटाकर 0 डीबी लाभ या उससे भी कम करने की आवश्यकता होती है।[9]

[10] इस डिज़ाइन के साथ एम्पलीफायर स्थिर है और इसमें लगभग-इष्टतम चरण प्रतिक्रिया #एकता लाभ वोल्टेज बफर के रूप में भी ओवरशूट का नियंत्रण है। एक अधिक आक्रामक तकनीक दो-ध्रुव मुआवजा है।[11][12] एफ की स्थिति का तरीका2 डिज़ाइन प्राप्त करने के लिए चित्र 3 में दिखाया गया है। सबसे निचले ध्रुव पर एफ1, बोडे गेन प्लॉट ढलान को तोड़कर 20 डीबी/दशक पर गिर जाता है। इसका उद्देश्य 20 डीबी/दशक ढलान को शून्य डीबी तक बनाए रखना है, और 20 लॉग के लाभ (डीबी में) में वांछित गिरावट का अनुपात लेना है।10 Avआवृत्ति में आवश्यक परिवर्तन के लिए (लॉग आवृत्ति पैमाने पर)।[13]) का ( लॉग10 f2 − लॉग10 f1 ) = लॉग10 ( एफ2 / एफ1 ) एफ के बीच खंड का ढलान1 और एफ2 है:

- आवृत्ति के प्रति दशक ढलान

जो कि 20 डीबी/दशक है बशर्ते कि एफ2 = एv f1. यदि एफ2यह इतना बड़ा नहीं है, बोड प्लॉट में दूसरा ब्रेक जो दूसरे ध्रुव पर होता है, लाभ 0 डीबी तक गिरने से पहले प्लॉट को बाधित करता है जिसके परिणामस्वरूप कम स्थिरता और ख़राब चरण प्रतिक्रिया होती है।

चित्र 3 से पता चलता है कि आवृत्ति पर सही लाभ निर्भरता प्राप्त करने के लिए, दूसरा ध्रुव कम से कम एक कारक ए हैvप्रथम ध्रुव की तुलना में आवृत्ति अधिक होती है। एम्पलीफायर के इनपुट और आउटपुट पर वोल्टेज डिवीजन#लोडिंग प्रभाव से लाभ थोड़ा कम हो जाता है, इसलिए ए में सुधार के साथvइनपुट और आउटपुट पर वोल्टेज डिवाइडर के लिए अच्छे चरण प्रतिक्रिया के लिए 'पोल-अनुपात स्थिति' बन जाती है:

ऊपर विकसित समय स्थिरांकों के लिए अनुमानों का उपयोग करते हुए,

या

जो C के लिए उचित मान निर्धारित करने के लिए एक द्विघात समीकरण प्रदान करता हैC. चित्र 4 इस समीकरण का उपयोग करके एक उदाहरण दिखाता है। लाभ के कम मूल्यों पर यह उदाहरण एम्पलीफायर मुआवजे के बिना ध्रुव-अनुपात की स्थिति को संतुष्ट करता है (अर्थात्, चित्र 4 में मुआवजा संधारित्र सीCकम लाभ पर छोटा है), लेकिन जैसे-जैसे लाभ बढ़ता है, क्षतिपूर्ति समाई तेजी से आवश्यक हो जाती है (अर्थात, चित्र 4 में क्षतिपूर्ति संधारित्र सीCलाभ के साथ तेजी से बढ़ता है) क्योंकि आवश्यक ध्रुव अनुपात लाभ के साथ बढ़ता है। अभी भी बड़े लाभ के लिए, आवश्यक सीCबढ़ते लाभ के साथ गिरता है क्योंकि सी का मिलर प्रवर्धनC, जो लाभ के साथ बढ़ता है (#Miller देखें), C के लिए एक छोटे मान की अनुमति देता हैC.

डिज़ाइन अनिश्चितताओं के लिए अधिक सुरक्षा मार्जिन प्रदान करने के लिए, अक्सर एvदो या तीन गुना ए तक बढ़ाया जाता हैvइस समीकरण के दाईं ओर.[14] सेंस देखें[4]या हुइज़िंग[10]और चरण प्रतिक्रिया पर लेख।

स्लिव दर

उपरोक्त एक लघु-संकेत विश्लेषण है। हालाँकि, जब बड़े सिग्नलों का उपयोग किया जाता है, तो क्षतिपूर्ति संधारित्र को चार्ज और डिस्चार्ज करने की आवश्यकता एम्पलीफायर स्लीव दर पर प्रतिकूल प्रभाव डालती है; विशेष रूप से, इनपुट रैंप सिग्नल की प्रतिक्रिया सी को चार्ज करने की आवश्यकता से सीमित होती हैC.

यह भी देखें

- आवृत्ति मुआवजा

- मिलर प्रभाव

- सामान्य स्रोत

- बोडे प्लॉट

- चरण प्रतिक्रिया#ओवरशूट का नियंत्रण

- सीएमओएस एम्पलीफायर

सन्दर्भ और नोट्स

- ↑ That is, the rise time is selected to be the fastest possible consistent with low overshoot and ringing.

- ↑

C. Toumazu, Moschytz GS & Gilbert B (Editors) (2007). Trade-offs in analog circuit design: the designer's companion. New York/Berlin/Dordrecht: Springer. pp. 272–275. ISBN 978-1-4020-7037-2.

{{cite book}}:|author=has generic name (help) - ↑ Marc T. Thompson (2006). Intuitive analog circuit design: a problem-solving approach using design case studies. Amsterdam: Elsevier Newnes. p. 200. ISBN 0-7506-7786-4.

- ↑ 4.0 4.1 Willy M. C. Sansen (2006). Analog design essentials. New York; Berlin: Springer. pp. §097, p. 266 et seq. ISBN 0-387-25746-2.

- ↑ Although this example appears very specific, the associated mathematical analysis is very much used in circuit design.

- ↑ The sum of the time constants is the coefficient of the term linear in jω and the product of the time constants is the coefficient of the quadratic term in (jω)2.

- ↑ The expression for differs a little from ( CM+Ci ) ( RA || Ri ) as found initially for f1, but the difference is minor assuming the load capacitance is not so large that it controls the low frequency response instead of the Miller capacitance.

- ↑ As an aside, the higher the high-frequency pole is made in frequency, the more likely it becomes for a real amplifier that other poles (not considered in this analysis) play a part.

- ↑ A.S. Sedra and K.C. Smith (2004). Microelectronic circuits (Fifth ed.). New York: Oxford University Press. pp. 849 and Example 8.6, p. 853. ISBN 0-19-514251-9.

- ↑ 10.0 10.1 Huijsing, Johan H. (2001). Operational amplifiers: theory and design. Boston, MA: Kluwer Academic. pp. §6.2, pp.205–206 and Figure 6.2.1. ISBN 0-7923-7284-0.

- ↑ Feucht, Dennis: Two-pole compensation

- ↑ Self, Douglas (2006). Audio power amplifier design handbook. Oxford: Newnes. pp. 191–193. ISBN 0-7506-8072-5.

- ↑ That is, the frequency is plotted in powers of ten, as 1, 10, 102 etc.

- ↑ A factor of two results in the maximally flat or Butterworth design for a two-pole amplifier. However, real amplifiers have more than two poles, and a factor greater than two often is necessary.

बाहरी संबंध

- Bode Plots in the Circuit Theory Wikibook

- Bode Plots in the Control Systems Wikibook