पता डिकोडर

डिजिटल इलेक्ट्रॉनिक्स में, एड्रेस डिकोडर एक बाइनरी डिकोडर होता है जिसमें पता बस बिट्स के लिए दो या अधिक इनपुट होते हैं और डिवाइस चयन सिग्नल के लिए एक या अधिक आउटपुट होते हैं।[1] जब किसी विशेष डिवाइस का पता एड्रेस इनपुट पर दिखाई देता है, तो डिकोडर उस डिवाइस के लिए चयन आउटपुट का दावा करता है। एक समर्पित, एकल-आउटपुट एड्रेस डिकोडर को एड्रेस बस के प्रत्येक डिवाइस में शामिल किया जा सकता है, या एक एकल एड्रेस डिकोडर कई डिवाइसों की सेवा कर सकता है।[2]

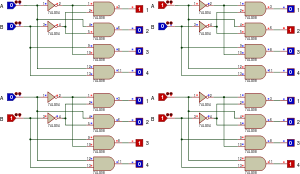

एन एड्रेस इनपुट बिट्स वाला एक सिंगल एड्रेस डिकोडर 2 तक काम कर सकता हैnडिवाइस. एकीकृत सर्किट के 7400 श्रृंखला एकीकृत सर्किट की सूची के कई सदस्यों को एड्रेस डिकोडर के रूप में उपयोग किया जा सकता है। उदाहरण के लिए, जब एड्रेस डिकोडर के रूप में उपयोग किया जाता है, तो 74154[3] चार पता इनपुट और सोलह (यानी, 2) प्रदान करता है4) डिवाइस चयनकर्ता आउटपुट। एड्रेस डिकोडर एक बाइनरी डिकोडर सर्किट का एक विशेष उपयोग है जिसे डीमल्टीप्लेक्सर या डिमक्स के रूप में जाना जाता है (74154 को आमतौर पर 4-टू-16 डिमल्टीप्लेक्सर कहा जाता है), जिसमें एड्रेस डिकोडिंग के अलावा कई अन्य उपयोग होते हैं।

एड्रेस डिकोडर बस (कंप्यूटिंग) का उपयोग करने वाले सिस्टम के लिए मूलभूत बिल्डिंग ब्लॉक हैं। वे सभी एकीकृत सर्किट परिवारों और प्रक्रियाओं और सभी मानक एफपीजीए और एप्लिकेशन-विशिष्ट एकीकृत सर्किट पुस्तकालयों में दर्शाए जाते हैं। डिजिटल लॉजिक डिज़ाइन में परिचयात्मक पाठ्यपुस्तकों में उनकी चर्चा की गई है।[1]

एड्रेस डिकोडर मेमोरी में स्टोरेज सेल का चयन करता है

एड्रेस डिकोडर माइक्रोइलेक्ट्रॉनिक्स में आमतौर पर इस्तेमाल किया जाने वाला घटक है जिसका उपयोग यादृच्छिक रूप से एड्रेस करने योग्य मेमोरी उपकरणों में मेमोरी कोशिकाओं का चयन करने के लिए किया जाता है।

ऐसी मेमोरी सेल में निश्चित संख्या में मेमोरी तत्व या बिट्स होते हैं। एड्रेस डिकोडर एक एड्रेस बस से जुड़ा होता है और वहां बनाए गए एड्रेस को पढ़ता है। एक विशेष स्विचिंग लॉजिक का उपयोग करते हुए, यह इस पते का उपयोग यह गणना करने के लिए करता है कि किस मेमोरी सेल को एक्सेस किया जाना है। फिर यह एक विशेष नियंत्रण रेखा के माध्यम से उस सेल का चयन करता है। इस लाइन को सेलेक्ट लाइन के नाम से भी जाना जाता है। गतिशील यादों (गतिशील रैंडम-एक्सेस मेमोरी ) में, मेमोरी मैट्रिक्स पर पंक्ति और स्तंभ चयन लाइनें होती हैं, जिन्हें चिप में एकीकृत एड्रेस डिकोडर द्वारा नियंत्रित किया जाता है।

डिकोडर के प्रकार के आधार पर, मेमोरी सेल का चयन करने के लिए उपयोग किया जाने वाला तर्क कुछ परिस्थितियों में प्रोग्राम करने योग्य हो सकता है।

एड्रेस डिकोडर उपयुक्त मेमोरी मॉड्यूल का चयन करता है

जब प्रोसेसर सिस्टम के एड्रेस बस द्वारा एक विशेष पता प्रदान किया जाता है, तो एक एड्रेस डिकोडर का उपयोग कई मेमोरी मॉड्यूल या मेमोरी चिप्स में से उपयुक्त एक का चयन करने के लिए भी किया जाता है।

इस उद्देश्य के लिए, मेमोरी मॉड्यूल या मेमोरी चिप्स में चयन इनपुट होते हैं, जिन्हें आमतौर पर चिप सेलेक्ट पिन (सीएस) या चिप इनेबल पिन (सीई) पिन कहा जाता है। इन इनपुट में अक्सर नकारात्मक तर्क फ़ंक्शन होता है (CS या CE), मैं। एच. आसन्न तार्किक शून्य (वोल्टेज स्तर कम) के साथ चुना गया है।

एड्रेस डिकोडर मेमोरी मॉड्यूल या चिप्स को प्रोसेसर के एड्रेस स्पेस में रखने के लिए अलग-अलग कॉम्बिनेटरियल लॉजिक का उपयोग करता है। मेमोरी मॉड्यूल में अक्सर एड्रेस स्पेस की तुलना में छोटी क्षमता होती है। ज्यादातर मामलों में, कई मॉड्यूल का उपयोग किया जा सकता है, भले ही वे संरचना में पूरी तरह से समान हों। यह सुनिश्चित किया जाना चाहिए कि वे पता सीमा में भिन्न हों।

संदर्भ

- ↑ 1.0 1.1 Paul Horowitz and Winfield Hill (1989). The Art of Electronics (2nd ed.). Cambridge University Press. p. 685,766. ISBN 978-0-521-37095-0.

- ↑ S. J. Cahill (1993). Digital and microprocessor engineering (2nd ed.). Ellis Horwood. pp. 489–494. ISBN 978-0-13-213398-2.

- ↑ Datasheet for 74HCT154