शिफ्ट का रजिस्टर

एक शिफ्ट रजिस्टर फ्लिप-फ्लॉप (इलेक्ट्रॉनिक्स) | फ्लिप-फ्लॉप के कैस्केड का उपयोग करके एक प्रकार का डिजिटल सर्किट है जहां एक फ्लिप-फ्लॉप का आउटपुट अगले के इनपुट से जुड़ा होता है। वे एक एकल घड़ी संकेत साझा करते हैं, जिसके कारण सिस्टम में संग्रहीत डेटा एक स्थान से दूसरे स्थान पर स्थानांतरित हो जाता है। अंतिम फ्लिप-फ्लॉप को वापस पहले से जोड़कर, डेटा शिफ्टर्स के भीतर विस्तारित अवधि के लिए चक्रित हो सकता है, और इस कॉन्फ़िगरेशन में उन्हें स्मृति के रूप में उपयोग किया जाता था, जो 1960 के दशक के अंत और 1970 के दशक की शुरुआत में विलंब-रेखा स्मृति सिस्टम को विस्थापित करता था।

ज्यादातर मामलों में, कई समांतर शिफ्ट रजिस्टरों का उपयोग एक बड़ा मेमोरी पूल बनाने के लिए किया जाएगा जिसे बिट सरणी के रूप में जाना जाता है। डेटा को सरणी में संग्रहीत किया गया था और समानांतर में वापस पढ़ा गया था, अक्सर एक कंप्यूटर शब्द के रूप में, जबकि प्रत्येक बिट को शिफ्ट रजिस्टरों में क्रमिक रूप से संग्रहीत किया गया था। बिट सरणियों के डिजाइन में एक अंतर्निहित व्यापार-बंद है; एक पंक्ति में अधिक फ्लिप-फ्लॉप रखने से एकल शिफ्टर को अधिक बिट्स स्टोर करने की अनुमति मिलती है, लेकिन डेटा को फिर से वापस पढ़ने से पहले सभी शिफ्टर्स के माध्यम से डेटा को पुश करने के लिए अधिक घड़ी चक्र की आवश्यकता होती है।

शिफ्ट रजिस्टर में समानांतर संचार और धारावाहिक संचार इनपुट और आउटपुट दोनों हो सकते हैं। इन्हें अक्सर सीरियल-इन, समानांतर-आउट (SIPO) या समानांतर-इन, सीरियल-आउट (PISO) के रूप में कॉन्फ़िगर किया जाता है। ऐसे भी प्रकार हैं जिनमें सीरियल और समांतर इनपुट और धारावाहिक और समांतर आउटपुट वाले प्रकार दोनों होते हैं। द्विदिश शिफ्ट रजिस्टर भी हैं, जो दोनों दिशाओं में शिफ्टिंग की अनुमति देते हैं: L → R या R → L। एक शिफ्ट रजिस्टर के सीरियल इनपुट और अंतिम आउटपुट को एक सर्कुलर शिफ्ट रजिस्टर बनाने के लिए भी जोड़ा जा सकता है। एक PIPO रजिस्टर (समानांतर इन, समानांतर आउट) बहुत तेज़ है - एक सिंगल क्लॉक पल्स के भीतर एक आउटपुट दिया जाता है।

सीरियल-इन सीरियल-आउट (एसआईएसओ)

विनाशकारी रीडआउट

| 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 1 | 0 | 1 | 0 |

| 4 | 1 | 1 | 0 | 1 |

| 5 | 0 | 1 | 1 | 0 |

| 6 | 0 | 0 | 1 | 1 |

| 7 | 0 | 0 | 0 | 1 |

| 8 | 0 | 0 | 0 | 0 |

ये सबसे सरल प्रकार के शिफ्ट रजिस्टर हैं। डेटा स्ट्रिंग को डेटा में प्रस्तुत किया जाता है और प्रत्येक बार डेटा अग्रिम को तर्क स्तर पर लाए जाने पर एक चरण में स्थानांतरित कर दिया जाता है। प्रत्येक अग्रिम पर, सबसे बाईं ओर का बिट (यानी डेटा में) पहले फ्लिप-फ्लॉप (इलेक्ट्रॉनिक्स) | फ्लिप-फ्लॉप के आउटपुट में स्थानांतरित हो जाता है। सबसे दाईं ओर का बिट (यानी डेटा आउट ) बाहर स्थानांतरित हो गया है और खो गया है।

क्यू आउटपुट पर प्रत्येक फ्लिप-फ्लॉप के बाद डेटा संग्रहीत किया जाता है, इसलिए इस व्यवस्था में चार स्टोरेज स्लॉट उपलब्ध हैं, इसलिए यह 4-बिट रजिस्टर है। शिफ्टिंग पैटर्न का अंदाजा लगाने के लिए, कल्पना करें कि रजिस्टर 0000 रखता है (इसलिए सभी स्टोरेज स्लॉट खाली हैं)। जैसा कि रजिस्टर में डेटा 1,0,1,1,0,0,0,0 प्रस्तुत करता है (उस क्रम में, डेटा पर एक पल्स के साथ हर बार आगे बढ़ता है - इसे क्लॉकिंग या स्ट्रोबिंग कहा जाता है), यह परिणाम है। दाहिने हाथ का कॉलम सबसे दाहिने फ्लिप-फ्लॉप के आउटपुट पिन से मेल खाता है, और इसी तरह।

तो पूरे रजिस्टर का सीरियल आउटपुट 00010110 है। यह देखा जा सकता है कि अगर डेटा को इनपुट करना जारी रखा जाता है, तो यह ठीक वही मिलेगा जो (10110000) में डाला गया था, लेकिन चार डेटा अग्रिम चक्रों द्वारा ऑफसेट किया गया। यह व्यवस्था कतार (डेटा संरचना) के हार्डवेयर समतुल्य है। साथ ही, किसी भी समय रीसेट (आर) पिन को ऊपर लाकर पूरे रजिस्टर को शून्य पर सेट किया जा सकता है।

यह व्यवस्था विनाशकारी रीडआउट करती है – प्रत्येक डेटाम एक बार खो जाता है जब इसे दाएँ-सबसे बिट से बाहर स्थानांतरित कर दिया जाता है।

सीरियल-इन समानांतर-आउट (SIPO)

यह कॉन्फ़िगरेशन सीरियल से समांतर प्रारूप में रूपांतरण की अनुमति देता है। डेटा इनपुट सीरियल है, जैसा कि ऊपर SISO सेक्शन में बताया गया है। एक बार डेटा क्लॉक हो जाने के बाद, इसे या तो प्रत्येक आउटपुट पर एक साथ पढ़ा जा सकता है, या इसे स्थानांतरित किया जा सकता है।

इस कॉन्फ़िगरेशन में, प्रत्येक फ्लिप-फ्लॉप संकेत किनारा है। सभी फ्लिप-फ्लॉप दिए गए क्लॉक फ्रीक्वेंसी पर काम करते हैं। प्रत्येक इनपुट बिट N घड़ी चक्र के बाद Nth आउटपुट के लिए अपना रास्ता बनाता है, जिससे समानांतर आउटपुट होता है।

ऐसे मामलों में जहां सीरियल लोडिंग प्रक्रिया के दौरान समांतर आउटपुट नहीं बदलना चाहिए, लैच्ड या डेटा बफ़र आउटपुट का उपयोग करना वांछनीय है। लैच्ड शिफ्ट रजिस्टर (जैसे कि 7400 श्रृंखला एकीकृत परिपथों की सूची) में सीरियल डेटा को पहले एक आंतरिक बफर रजिस्टर में लोड किया जाता है, फिर लोड सिग्नल प्राप्त होने पर बफर रजिस्टर की स्थिति को आउटपुट रजिस्टरों के एक सेट में कॉपी किया जाता है। सामान्य तौर पर, सीरियल-इन / समांतर-आउट शिफ्ट रजिस्टर का व्यावहारिक अनुप्रयोग डेटा को सीरियल प्रारूप से एक तार पर समानांतर प्रारूप में कई तारों पर परिवर्तित करना है।

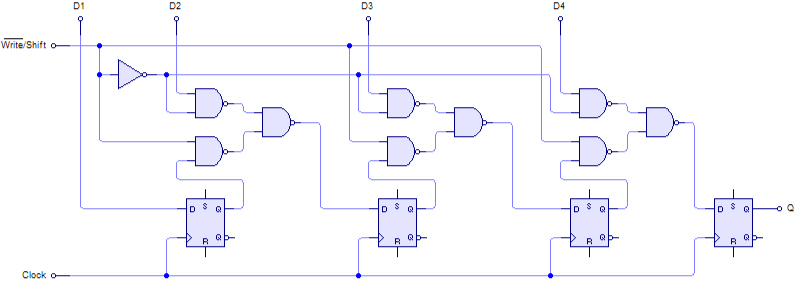

समानांतर-इन सीरियल-आउट (PISO)

इस कॉन्फ़िगरेशन में समानांतर प्रारूप में D1 से D4 तक डेटा इनपुट है, D1 सबसे महत्वपूर्ण बिट है। रजिस्टर में डेटा लिखने के लिए, राइट/शिफ्ट कंट्रोल लाइन को कम रखना चाहिए। डेटा को स्थानांतरित करने के लिए, W/S control line is brought HIGH and the registers are clocked. The arrangement now acts as a PISO shift register, with D1 as the Data Input. However, as long as the number of clock cycles is not more than the length of the data-string, the Data Output, Q, will be the parallel data read off in order.

नीचे दिया गया एनीमेशन लेखन दिखाता है/shift sequence, including the internal state of the shift register.

उपयोग करता है

शिफ्ट रजिस्टर के सबसे आम उपयोगों में से एक सीरियल और समांतर इंटरफेस के बीच कनवर्ट करना है। यह उपयोगी है क्योंकि कई सर्किट समानांतर में बिट्स के समूह पर काम करते हैं, लेकिन सीरियल इंटरफेस निर्माण के लिए आसान होते हैं। शिफ्ट रजिस्टरों का उपयोग सरल विलंब सर्किट के रूप में किया जा सकता है। स्टैक (डेटा संरचना) के हार्डवेयर कार्यान्वयन के लिए कई द्विदिश शिफ्ट रजिस्टरों को समानांतर में जोड़ा जा सकता है।

SIPO रजिस्टर आमतौर पर माइक्रोप्रोसेसरों के आउटपुट से जुड़े होते हैं जब अधिक सामान्य-उद्देश्य इनपुट/आउटपुट पिन उपलब्ध होने की तुलना में आवश्यक होते हैं। यह कई बाइनरी उपकरणों को केवल दो या तीन पिनों का उपयोग करके नियंत्रित करने की अनुमति देता है, लेकिन समानांतर आउटपुट की तुलना में अधिक धीरे-धीरे। विचाराधीन उपकरण शिफ्ट रजिस्टर के समानांतर आउटपुट से जुड़े होते हैं, और उन सभी उपकरणों के लिए वांछित स्थिति को एकल सीरियल कनेक्शन का उपयोग करके माइक्रोप्रोसेसर से बाहर भेजा जा सकता है। इसी तरह, पीआईएसओ कॉन्फ़िगरेशन आमतौर पर माइक्रोप्रोसेसर में उपलब्ध बाइनरी इनपुट की तुलना में अधिक बाइनरी इनपुट जोड़ने के लिए उपयोग किया जाता है - प्रत्येक बाइनरी इनपुट (जैसे बटन या अधिक जटिल सर्किटरी) शिफ्ट रजिस्टर के समानांतर इनपुट से जुड़ा होता है, फिर डेटा को वापस भेजा जाता है मूल रूप से आवश्यकता से कई कम लाइनों का उपयोग करके माइक्रोप्रोसेसर को सीरियल।

शिफ्ट रजिस्टर का उपयोग पल्स एक्सटेंडर के रूप में भी किया जा सकता है। मोनोस्टेबल मल्टीवीब्रेटर्स की तुलना में, समय घटक मूल्यों पर निर्भर नहीं करता है, लेकिन इसके लिए एक बाहरी घड़ी की आवश्यकता होती है, और समय की सटीकता इस घड़ी की ग्रैन्युलैरिटी द्वारा सीमित होती है। ऐसे पल्स एक्सटेंडर का एक उदाहरण रोंजा ट्विस्टर है, जिसमें पांच List_of_7400-series_integrated_circuits#74x100_–_74x199 टाइमिंग लॉजिक के मूल को इस तरह बनाते हैं (योजनाबद्ध)।

शुरुआती कंप्यूटरों में, डेटा प्रोसेसिंग को संभालने के लिए शिफ्ट रजिस्टरों का उपयोग किया जाता था: जोड़े जाने वाले दो नंबरों को दो शिफ्ट रजिस्टरों में संग्रहीत किया जाता था और एक अंकगणितीय तर्क इकाई में जोड़ा जाता था। शिफ्ट रजिस्टरों (संचायक) में से एक, जो एक सा लंबा था, क्योंकि बाइनरी जोड़ का परिणाम केवल उसी उत्तर में हो सकता है जिसका आकार समान हो या एक बिट लंबा हो।

कई कंप्यूटर भाषाओं में एक रजिस्टर में डेटा को दाएं और बाएं स्थानांतरित करने के निर्देश शामिल हैं, प्रत्येक स्थानांतरित स्थान के लिए प्रभावी रूप से दो से विभाजित या दो से गुणा करना।

बहुत बड़े सीरियल-इन सीरियल-आउट शिफ्ट रजिस्टर (हजारों बिट्स आकार में) का उपयोग 1970 के दशक की शुरुआत में निर्मित कुछ उपकरणों में पहले की देरी-लाइन मेमोरी के समान तरीके से किया गया था। ऐसी स्मृतियों को कभी-कभी परिसंचारी स्मृति कहा जाता था। उदाहरण के लिए, डेटापॉइंट 3300 टर्मिनल ने प्रति पंक्ति वर्णों की 25 पंक्तियों का अपना प्रदर्शन संग्रहीत किया| 54 200-बिट शिफ्ट रजिस्टरों (9 पैक के 6 ट्रैक में व्यवस्थित) का उपयोग करके 6-बिट अपर-केस वर्णों के 72 कॉलम, 1800 वर्णों के लिए संग्रहण प्रदान करते हैं . शिफ्ट रजिस्टर डिज़ाइन का मतलब था कि टर्मिनल डिस्प्ले को स्क्रॉल करना वर्णों की एक पंक्ति को छोड़ने के लिए डिस्प्ले आउटपुट को रोककर पूरा किया जा सकता है।[1]

इतिहास

शिफ्ट रजिस्टर के पहले ज्ञात उदाहरणों में से एक मार्क 2 बादशाह कंप्यूटर में था, जो 1944 में निर्मित एक कोड-ब्रेकिंग मशीन थी। यह वेक्यूम - ट्यूब और थाइरेट्रॉन से निर्मित छह-चरण का उपकरण था।[2] 1940 के अंत में उन्नत अध्ययन संस्थान में जॉन वॉन न्यूमैन और अन्य द्वारा निर्मित IAS मशीन में एक शिफ्ट रजिस्टर का भी उपयोग किया गया था। 1960 के दशक में शिफ्ट रजिस्टरों ने एकीकृत परिपथों में अपना रास्ता बनाया, जैसा कि फ्रैंक वानलास के शुरुआती पेटेंटों से पता चलता है[3] और केंट स्मिथ[4] सामान्य साधन में कार्यरत

यह भी देखें

- विलंब-रेखा स्मृति

- लीनियर-फीडबैक शिफ्ट रजिस्टर (एलएफएसआर)

- रिंग काउंटर

- SerDes (सीरियलाइज़र/डेसेरिएलाइज़र)

- सीरियल पेरिफेरल इंटरफेस बस

- शिफ्ट रजिस्टर लुकअप टेबल (SRL)

- गोलाकार बफर

संदर्भ

- ↑ bitsavers.org, DataPoint 3300 Maintenance Manual, December 1976.

- ↑ Flowers, Thomas H. (1983), "The Design of Colossus", Annals of the History of Computing, 5 (3): 246, doi:10.1109/MAHC.1983.10079, S2CID 39816473

- ↑ https://patents.google.com/patent/US3406346A/en

- ↑ https://patents.google.com/patent/US3683203

- Templates that generate short descriptions

- Collapse templates

- Navigational boxes

- Navigational boxes without horizontal lists

- Sidebars with styles needing conversion

- Templates generating microformats

- Templates that are not mobile friendly

- Wikipedia metatemplates

- डिजिटल रजिस्टर

- स्मृति

- Machine Translated Page

- Created On 31/05/2023