अल्फ़ा 21264

अल्फा 21264 एक डिजिटल उपकरण निगम जोखिम माइक्रोप्रोसेसर है जिसे 19 अक्टूबर 1998 को लॉन्च किया गया था। 21264 ने डीईसी अल्फा अनुदेश सेट वास्तुकला (आईएसए) लागू किया।

विवरण

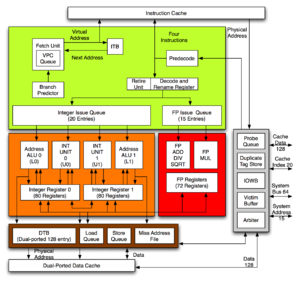

अल्फ़ा 21264 एक चार अंक वाला सुपरस्केलर माइक्रोप्रोसेसर है जिसमें आउट-ऑफ़-ऑर्डर निष्पादन और सट्टा निष्पादन है। इसकी सर्वोच्च निष्पादन दर प्रति चक्र छह निर्देशों की है और यह प्रति चक्र चार निर्देशों को बनाए रख सकती है। इसमें सात चरणों वाली अनुदेश पाइपलाइन है।

ऑर्डर निष्पादन से बाहर

किसी भी चरण में, माइक्रोप्रोसेसर के पास निष्पादन के विभिन्न चरणों में 80 निर्देश हो सकते हैं, जो किसी भी अन्य समकालीन माइक्रोप्रोसेसर से आगे निकल सकते हैं।

डिकोड किए गए निर्देशों को निर्देश कतारों में रखा जाता है और उनके ऑपरेंड उपलब्ध होने पर जारी किए जाते हैं। पूर्णांक कतार में 20 प्रविष्टियाँ और फ़्लोटिंग-पॉइंट कतार में 15 शामिल थे। प्रत्येक कतार उतने ही निर्देश जारी कर सकती थी जितनी पाइपलाइनें थीं।

ईबॉक्स

ईबॉक्स पूर्णांक, लोड और स्टोर निर्देशों को निष्पादित करता है। इसमें दो पूर्णांक इकाइयाँ, दो लोड स्टोर इकाइयाँ और दो पूर्णांक फ़ाइल पंजीकृत करेंें हैं। प्रत्येक पूर्णांक रजिस्टर फ़ाइल में 80 प्रविष्टियाँ थीं, जिनमें से 32 वास्तुशिल्प रजिस्टर हैं, 40 नाम बदलें रजिस्टर हैं और 8 PAL छाया रजिस्टर हैं। रजिस्टर R31 के लिए कोई प्रविष्टि नहीं थी क्योंकि अल्फा आर्किटेक्चर में, R31 को शून्य पर हार्डवायर किया गया है और केवल पढ़ने के लिए है।

प्रत्येक रजिस्टर फ़ाइल एक पूर्णांक इकाई और एक लोड स्टोर इकाई प्रदान करती है, और रजिस्टर फ़ाइल और इसकी दो इकाइयों को क्लस्टर के रूप में संदर्भित किया जाता है। दो समूहों को U0 और U1 नामित किया गया था। इस योजना का उपयोग इसलिए किया गया क्योंकि इससे ऑपरेंड की सेवा और परिणाम प्राप्त करने के लिए आवश्यक लिखने और पढ़ने वाले पोर्ट की संख्या कम हो गई, इस प्रकार रजिस्टर फ़ाइल का भौतिक आकार कम हो गया, जिससे माइक्रोप्रोसेसर उच्च घड़ी आवृत्तियों पर काम करने में सक्षम हो गया। इस प्रकार किसी भी रजिस्टर फ़ाइल को लिखने को सिंक्रनाइज़ करना पड़ता है, जिसे पूरा करने के लिए एक घड़ी चक्र की आवश्यकता होती है, जिससे प्रदर्शन पर एक प्रतिशत का नकारात्मक प्रभाव पड़ता है। सिंक्रनाइज़ेशन के परिणामस्वरूप प्रदर्शन में कमी की भरपाई दो तरीकों से की गई। सबसे पहले, उच्च घड़ी आवृत्ति प्राप्त होने से नुकसान की भरपाई हो जाती है। दूसरे, निर्देश जारी करने के लिए जिम्मेदार तर्क ने उन स्थितियों को बनाने से परहेज किया जहां रजिस्टर फ़ाइल को ऐसे निर्देश जारी करके सिंक्रनाइज़ करना पड़ता था जो जहां संभव हो अन्य रजिस्टर फ़ाइल में रखे गए डेटा पर निर्भर नहीं थे।

दो अंतरों को छोड़कर क्लस्टर लगभग समान हैं: U1 में सात-चक्र पाइपलाइन गुणक है जबकि U0 में मोशन वीडियो निर्देश (एमवीआई) निष्पादित करने के लिए तीन-चक्र पाइपलाइन है, जो एकल निर्देश एकाधिक डेटा (SIMD) निर्देशों को परिभाषित करने वाले अल्फा आर्किटेक्चर का विस्तार है। मल्टीमीडिया के लिए.

लोड स्टोर इकाइयाँ सरल अंकगणितीय तर्क इकाइयाँ हैं जिनका उपयोग मेमोरी एक्सेस के लिए वर्चुअल पतों की गणना करने के लिए किया जाता है। वे सरल अंकगणित और तर्क निर्देशों को क्रियान्वित करने में भी सक्षम हैं। अल्फ़ा 21264 निर्देश समस्या तर्क ने इस क्षमता का उपयोग किया, इन इकाइयों को निर्देश जारी किए जब वे उपयोग के लिए उपलब्ध थे (पता अंकगणित नहीं कर रहे थे)।

इसलिए ईबॉक्स में चार 64-बिट योजक (इलेक्ट्रॉनिक्स) एस, चार लॉजिक इकाइयां, दो बैरल शिफ्टर्स, बाइट-हेरफेर लॉजिक, सशर्त शाखा लॉजिक के दो सेट समान रूप से यू 1 और यू 0 के बीच विभाजित हैं।

एफबॉक्स

Fbox तैरनेवाला स्थल निर्देशों को निष्पादित करने के लिए ज़िम्मेदार है। इसमें दो फ़्लोटिंग-पॉइंट पाइपलाइन और एक फ़्लोटिंग-पॉइंट रजिस्टर फ़ाइल शामिल है। पाइपलाइनें समान नहीं हैं, एक अधिकांश निर्देशों को निष्पादित करता है और दूसरा केवल निर्देशों को गुणा करता है। योजक पाइपलाइन में दो गैर-पाइपलाइन इकाइयां जुड़ी हुई हैं, एक डिवाइड इकाई और एक वर्गमूल इकाई। जोड़ता है, गुणा करता है और अधिकांश अन्य निर्देशों में 4-चक्र विलंबता होती है, एक डबल-सटीक विभाजन में 16-चक्र विलंबता होती है और एक डबल-सटीक वर्गमूल में 33-चक्र विलंबता होती है। फ़्लोटिंग पॉइंट रजिस्टर फ़ाइल में 72 प्रविष्टियाँ हैं, जिनमें से 32 वास्तुशिल्प रजिस्टर हैं और 40 नाम बदलें रजिस्टर हैं।

कैश

अल्फ़ा 21264 में सीपीयू कैश के दो स्तर हैं, एक प्राथमिक कैश और द्वितीयक कैश। बैंडविड्थ की समस्याओं के कारण अल्फ़ा 21164 के स्तर तीन (एल3, या पीड़ित) कैश का उपयोग नहीं किया गया था।

प्राथमिक कैश

प्राथमिक कैश को क्रमशः निर्देशों और डेटा (संशोधित हार्वर्ड आर्किटेक्चर), आई-कैश और डी-कैश के लिए अलग-अलग कैश में विभाजित किया गया है। दोनों कैश की क्षमता 64 KB है। डी-कैश क्लॉक सिग्नल के बढ़ते और गिरते दोनों किनारों पर डेटा स्थानांतरित करके दोहरे पोर्ट वाला है। दोहरे पोर्टिंग की इस पद्धति ने प्रत्येक प्रोसेसर चक्र में कैश में पढ़ने या लिखने के किसी भी संयोजन को सक्षम किया। इससे कैश के दोहराव से भी बचा जा सकता है, इसलिए दो हैं, जैसा कि अल्फ़ा 21164 में है। कैश को डुप्लिकेट करने से कैश की क्षमता सीमित हो जाती है, क्योंकि समान मात्रा में क्षमता प्रदान करने के लिए अधिक ट्रांजिस्टर की आवश्यकता होती है, और बदले में आवश्यक क्षेत्र और बिजली की खपत बढ़ जाती है। .

बी-कैश

द्वितीयक कैश, जिसे बी-कैश कहा जाता है, 1 से 16 एमबी की क्षमता वाला एक बाहरी कैश है। इसे माइक्रोप्रोसेसर द्वारा नियंत्रित किया जाता है और सिंक्रोनस स्थैतिक रैंडम एक्सेस मेमोरी (एसएसआरएएम) चिप्स द्वारा कार्यान्वित किया जाता है जो दो तिहाई, आधे, एक तिहाई या एक-चौथाई आंतरिक घड़ी आवृत्ति या 500 मेगाहर्ट्ज पर 133 से 333 मेगाहर्ट्ज पर काम करता है। बी-कैश को एक समर्पित 128-बिट बस के साथ एक्सेस किया गया था जो SSRAM के समान घड़ी आवृत्ति पर या डबल डेटा दर SSRAM का उपयोग करने पर दोगुनी आवृत्ति पर संचालित होता है। बी-कैश डायरेक्ट-मैप किया गया है।[1]

शाखा भविष्यवाणी

शाखा भविष्यवक्ता एक टूर्नामेंट शाखा भविष्यवाणी एल्गोरिथ्म द्वारा किया जाता है। एल्गोरिदम को स्कॉट मैकफ़ार्लिंग द्वारा डिजिटल वेस्टर्न रिसर्च लेबोरेटरी (डब्ल्यूआरएल) में विकसित किया गया था और 1993 के एक पेपर में इसका वर्णन किया गया था। इस भविष्यवक्ता का उपयोग इसलिए किया गया क्योंकि अल्फा 21264 में सात चक्रों का न्यूनतम शाखा गलत पूर्वानुमान दंड है। निर्देश कैश की दो चक्र विलंबता और निर्देश कतारों के कारण, औसत शाखा गलत पूर्वानुमान जुर्माना 11 चक्र है। एल्गोरिथ्म दो इतिहास तालिकाओं, स्थानीय और वैश्विक को बनाए रखता है, और एक शाखा के परिणाम की भविष्यवाणी करने के लिए उपयोग की जाने वाली तालिका एक चॉइस भविष्यवक्ता द्वारा निर्धारित की जाती है।

स्थानीय भविष्यवक्ता एक दो-स्तरीय तालिका है जो व्यक्तिगत शाखाओं के इतिहास को रिकॉर्ड करती है। इसमें 10-बिट शाखा इतिहास तालिका द्वारा 1,024-प्रविष्टि शामिल है। दो-स्तरीय तालिका का उपयोग किया गया था क्योंकि भविष्यवाणी सटीकता एक बड़ी एकल-स्तरीय तालिका के समान होती है, जबकि भंडारण के कम बिट्स की आवश्यकता होती है। इसमें 1,024-प्रवेश शाखा भविष्यवाणी तालिका है। प्रत्येक प्रविष्टि एक 3-बिट संतृप्त काउंटर है। काउंटर का मूल्य निर्धारित करता है कि वर्तमान शाखा ली गई है या नहीं ली गई है।

वैश्विक भविष्यवक्ता एक एकल-स्तरीय, 4096-प्रविष्टि शाखा इतिहास तालिका है। प्रत्येक प्रविष्टि 2-बिट संतृप्त काउंटर है; इस काउंटर का मूल्य यह निर्धारित करता है कि वर्तमान शाखा ली गई है या नहीं ली गई है।

चयन भविष्यवक्ता यह निर्धारित करने के लिए स्थानीय और वैश्विक भविष्यवक्ताओं के इतिहास को रिकॉर्ड करता है कि किसी विशेष शाखा के लिए कौन सा भविष्यवक्ता सबसे अच्छा है। इसमें 4,096-प्रवेश शाखा इतिहास तालिका है। प्रत्येक प्रविष्टि 2-बिट संतृप्त काउंटर है। काउंटर का मान यह निर्धारित करता है कि स्थानीय या वैश्विक भविष्यवक्ता का उपयोग किया जाता है या नहीं।

बाहरी इंटरफ़ेस

बाहरी इंटरफ़ेस में एक द्विदिश 64-बिट डबल डेटा रेट (डीडीआर) बस (कंप्यूटिंग) और दो 15-बिट यूनिडायरेक्शनल टाइम-मल्टीप्लेक्स पता बस और नियंत्रण बस बसें शामिल थीं, एक अल्फा 21264 से उत्पन्न होने वाले सिग्नल के लिए और एक अल्फा 21264 से आने वाले सिग्नल के लिए। प्रणाली। डिजिटल ने बस को उन्नत लघु उपकरण (एएमडी) को लाइसेंस दिया, और बाद में इसका उपयोग उनके Athlon माइक्रोप्रोसेसरों में किया गया, जहां इसे ईवी 6 बस के रूप में जाना जाता था।

स्मृति संबोधन

अल्फा 21264 सीपीयू 48-बिट या 43-बिट वर्चुअल एड्रेस (क्रमशः 256 टीआईबी या 8 टीआईबी वर्चुअल एड्रेस स्पेस) का समर्थन करता है, जिसे आईपीआर नियंत्रण (वीए_सीटीएल नियंत्रण रजिस्टर का उपयोग करके) के तहत चयन किया जा सकता है। अल्फ़ा 21264 44-बिट भौतिक पते (भौतिक मेमोरी के 16 टीआईबी तक) का समर्थन करता है। यह पिछले अल्फा सीपीयू (अल्फा 21164 के लिए 43-बिट वर्चुअल और 40-बिट फिजिकल, और अल्फ़ा 21064 के लिए 43-बिट वर्चुअल और 34-बिट फिजिकल) से वृद्धि है।[2]

निर्माण

अल्फ़ा 21264 में 15.2 मिलियन ट्रांजिस्टर थे। तर्क में लगभग छह मिलियन ट्रांजिस्टर शामिल थे, बाकी कैश और शाखा इतिहास तालिकाओं में निहित थे। डाई की माप 16.7 मिमी गुणा 18.8 मिमी (313.96 मिमी²) थी।[3] इसे 0.35 μm CMOS|पूरक धातु-ऑक्साइड-सेमीकंडक्टर (CMOS) सेमीकंडक्टर डिवाइस निर्माण में इंटरकनेक्ट के छह स्तरों के साथ निर्मित किया गया था।

पैकेजिंग

अल्फ़ा 21264 को 587-पिन सिरेमिक इंटरस्टिशियल पिन ग्रिड सरणी (आईपीजीए) में पैक किया गया था।

अल्फा प्रोसेसर, इंक. ने बाद में अल्फा 21264 को स्लॉट बी पैकेज में बेचा, जिसमें बी-कैश और वोल्टेज नियामकों के साथ एक मुद्रित सर्किट बोर्ड पर लगा माइक्रोप्रोसेसर था। डिज़ाइन का उद्देश्य इंटेल और एएमडी के स्लॉट-आधारित माइक्रोप्रोसेसरों की सफलता का उपयोग करना था। स्लॉट बी को मूल रूप से एएमडी के एथलॉन द्वारा उपयोग करने के लिए विकसित किया गया था, ताकि एपीआई व्यापक बाजार हिस्सेदारी हासिल करने के लिए अल्फा 21264 की लागत को कम करने के लिए कमोडिटी कीमतों पर स्लॉट बी के लिए सामग्री प्राप्त कर सके। यह कभी साकार नहीं हुआ क्योंकि एएमडी ने अपने स्लॉट-आधारित एथलॉन के लिए स्लॉट ए का उपयोग करना चुना।

व्युत्पन्न

अल्फा 21264ए

अल्फा 21264ए, कोड-नाम ईवी67, 1999 के अंत में पेश किए गए अल्फा 21264 का संक्षिप्त रूप था। इसके छह संस्करण थे: 600, 667, 700, 733, 750, 833 मेगाहर्ट्ज। EV67 काउंट एक्सटेंशन (CIX) को लागू करने वाला पहला अल्फा माइक्रोप्रोसेसर था, जिसने हथौड़ा चलाना वजन प्रदर्शन के निर्देशों के साथ निर्देश सेट को बढ़ाया। इसे सैमसंग इलेक्ट्रॉनिक्स द्वारा 0.25 μm CMOS प्रक्रिया में निर्मित किया गया था जिसमें 0.25 μm ट्रांजिस्टर लेकिन 0.35 μm धातु की परतें थीं। डाई का क्षेत्रफल 210 मिमी² था। EV68 में 2.0 V बिजली आपूर्ति का उपयोग किया गया। इसने 600 मेगाहर्ट्ज पर अधिकतम 73 डब्ल्यू, 667 मेगाहर्ट्ज पर 80 डब्ल्यू, 700 मेगाहर्ट्ज पर 85 डब्ल्यू, 733 मेगाहर्ट्ज पर 88 डब्ल्यू और 750 मेगाहर्ट्ज पर 90 डब्ल्यू का अपव्यय किया।

अल्फा 21264बी

अल्फा 21264बी बढ़ी हुई घड़ी आवृत्तियों के लिए एक और विकास है। दो मॉडल थे, एक IBM द्वारा निर्मित, कोड-नाम EV68C, और एक सैमसंग द्वारा, कोड-नाम EV68A।

EV68A को एल्यूमीनियम इंटरकनेक्ट के साथ 0.18 μm CMOS प्रक्रिया में निर्मित किया गया था। इसका डाई आकार 125 मिमी² था, जो अल्फा 21264ए से एक तिहाई छोटा था, और इसमें 1.7 वी बिजली की आपूर्ति का उपयोग किया गया था। यह 2001 में 750, 833, 875 और 940 मेगाहर्ट्ज की घड़ी आवृत्तियों पर वॉल्यूम में उपलब्ध था। EV68A ने 750 मेगाहर्ट्ज पर अधिकतम 60 W, 833 मेगाहर्ट्ज पर 67 W, 875 मेगाहर्ट्ज पर 70 W और 940 मेगाहर्ट्ज पर 75 W का क्षय किया।[4] EV68C को कॉपर इंटरकनेक्ट के साथ 0.18 μm CMOS प्रक्रिया में निर्मित किया गया था। इसका नमूना 2000 की शुरुआत में लिया गया था और अधिकतम घड़ी की आवृत्ति 1.25 गीगाहर्ट्ज़ हासिल की गई थी।

सितंबर 1998 में, सैमसंग ने घोषणा की कि वे कॉपर-आधारित चिप्स के साथ 0.18 μm पूरी तरह से समाप्त सिलिकॉन-ऑन-इन्सुलेटर (SOI) प्रक्रिया में अल्फा 21264B का एक संस्करण तैयार करेंगे जो 1.5 GHz की घड़ी आवृत्ति प्राप्त करने में सक्षम था। यह संस्करण कभी साकार नहीं हुआ।

अल्फा 21264सी

अल्फा 21264C, कोड-नाम EV68CB, अल्फा 21264 का व्युत्पन्न था। यह 1.0, 1.25 और 1.33 GHz की घड़ी आवृत्तियों पर उपलब्ध था। EV68CB में 15.5 मिलियन ट्रांजिस्टर थे और इसकी माप 120 mm² थी। इसे IBM द्वारा 0.18 μm CMOS प्रक्रिया में कॉपर इंटरकनेक्ट और कम कश्मीर ढांकता हुआ के सात स्तरों के साथ निर्मित किया गया था। इसे 675-पैड पलटें काटना सिरेमिक भूमि ग्रिड सरणी (सीएलजीए) में पैक किया गया था, जिसकी माप 49.53 गुणा 49.53 मिमी थी। EV68CB ने 1.7 V बिजली आपूर्ति का उपयोग किया, जो 1.0 GHz पर अधिकतम 64 W, 1.25 GHz पर 75 W और 1.33 GHz पर 80 W का अपव्यय करता है।[5]

अल्फा 21264डी

अल्फ़ा 21264D, कोड-नाम EV68CD, IBM द्वारा निर्मित एक तेज़ व्युत्पन्न है।

अल्फा 21264ई

अल्फा 21264E, कोड-नाम EV68E, सैमसंग द्वारा विकसित एक रद्द किया गया व्युत्पन्न था जिसे पहली बार 10 अक्टूबर 2000 को माइक्रोप्रोसेसर फोरम 2000 में लगभग 2001 के मध्य में पेश करने की घोषणा की गई थी। सुधारों में 1.25 गीगाहर्ट्ज़ की उच्च ऑपरेटिंग आवृत्ति और ऑन-डाई 1.85 एमबी सेकेंडरी कैश को शामिल करना शामिल था। इसे कॉपर इंटरकनेक्ट के साथ 0.18 माइक्रोमीटर सीएमओएस प्रक्रिया में निर्मित किया जाना था।

चिपसेट

डिजिटल और एडवांस्ड माइक्रो डिवाइसेस (एएमडी) दोनों ने अल्फा 21264 के लिए चिपसेट विकसित किए।

21272/21274

डिजिटल 21272, जिसे सुनामी के नाम से भी जाना जाता है, और 21274, जिसे टाइफून के नाम से भी जाना जाता है, अल्फा 21264 के लिए पहला चिपसेट था। 21272 चिपसेट एक या दो-तरफा मल्टीप्रोसेसिंग और 8 जीबी तक मेमोरी का समर्थन करता था, जबकि 21274 एक-, दो-, तीन- या चार-तरफा मल्टीप्रोसेसिंग, 64 जीबी तक मेमोरी का समर्थन किया, और दोनों ने एक या दो 64-बिट 33 मेगाहर्ट्ज पेरिफ़ेरल कंपोनेंट इंटरकनेक्ट बसों का समर्थन किया। उनके पास 128- से 512-बिट मेमोरी बस थी जो 83 मेगाहर्ट्ज पर चलती थी, जिससे अधिकतम 5,312 एमबी/सेकेंड की बैंडविड्थ मिलती थी। चिपसेट 100 मेगाहर्ट्ज पंजीकृत ईसीसी एसडीआरएएम का समर्थन करता है।

चिपसेट में तीन डिवाइस शामिल थे, एक सी-चिप, एक डी-चिप और एक पी-चिप। चिपसेट बनाने वाले उपकरणों की संख्या अलग-अलग थी क्योंकि यह चिपसेट के कॉन्फ़िगरेशन द्वारा निर्धारित की गई थी। सी-चिप एक नियंत्रण चिप है जिसमें मेमोरी कंट्रोलर होता है। प्रत्येक माइक्रोप्रोसेसर के लिए एक सी-चिप की आवश्यकता थी।

पी-चिप पीसीआई नियंत्रक है, जो 33 मेगाहर्ट्ज पीसीआई बस को कार्यान्वित करता है। 21272 में एक या दो पी-चिप्स हो सकते हैं।

डी-चिप DRAM नियंत्रक है, जो सीपीयू से/तक और पी-चिप से/तक पहुंच लागू करता है। 21272 में दो या चार डी-चिप्स हो सकते हैं और 21274 में दो, चार या आठ डी-चिप्स हो सकते हैं।

21272 और 21274 का उपयोग डिजिटल, कॉम्पैक और हेवलेट पैकार्ड द्वारा उनके प्रवेश-स्तर से लेकर मध्य-श्रेणी के अल्फासर्वर और अल्फास्टेशन के सभी मॉडलों में बड़े पैमाने पर किया गया था। इसका उपयोग अल्फा प्रोसेसर, इंक. (जिसे बाद में एपीआई नेटवर्क के नाम से जाना गया) के तृतीय-पक्ष उत्पादों जैसे कि उनके UP2000+ मदरबोर्ड में भी किया गया था।

इरोंगेट

एएमडी ने दो अल्फा 21264-संगत चिपसेट विकसित किए, इरोंगेट, जिसे एएमडी-751 के रूप में भी जाना जाता है, और इसके उत्तराधिकारी, इरोंगेट-2, जिसे एएमडी-761 के रूप में भी जाना जाता है। ये चिपसेट उनके एथलॉन माइक्रोप्रोसेसरों के लिए विकसित किए गए थे, लेकिन एएमडी लाइसेंसिंग के कारण डिजिटल से अल्फा में उपयोग की जाने वाली ईवी 6 बस, एथलॉन और अल्फा 21264 बस प्रोटोकॉल के संदर्भ में संगत थे। आयरनगेट का उपयोग सैमसंग द्वारा अपने UP1000 और UP1100 मदरबोर्ड में किया गया था। आयरनगेट-2 का उपयोग सैमसंग ने अपने UP1500 मदरबोर्ड में किया था।

यह भी देखें

- अल्फावम: विंडोज़ या लिनक्स पर चलने वाला एक पूर्ण डीईसी अल्फ़ा सिस्टम एमुलेटर। इसमें अल्फा सीपीयू का एक उच्च-प्रदर्शन एमुलेटर शामिल है।

- बुलडोजर (माइक्रोआर्किटेक्चर)#सीएमटी|क्लस्टर मल्टी-थ्रेडिंग

- अल्फ़ा 21364

- अल्फ़ा 21464

टिप्पणियाँ

- ↑ The Alpha 21264 Microprocessor Architecture, p. 5.

- ↑ "Alpha 21264 Microprocessor Data Sheet" (PDF). Compaq Computer Corporation. Retrieved 2020-06-03.

- ↑ Gronowski, "High Performance Microprocessor Design", p. 676.

- ↑ Compaq, "21264/EV68A Microprocessor Hardware Reference Manual".

- ↑ Compaq, "21264/EV68CB and 21264/EV68DC Hardware Reference Manual".

संदर्भ

- Compaq Computer Corporation (July 1999). Alpha 21264 Microprocessor Hardware Reference Manual.

- Compaq Computer Corporation (June 2001). 21264/EV68CB and 21264/EV68DC Hardware Reference Manual.

- Compaq Computer Corporation (March 2002). 21264/EV67 Microprocessor Hardware Reference Manual.

- Compaq Computer Corporation (March 2002). 21264/EV68A Microprocessor Hardware Reference Manual.

- Gronowski, Paul E. et al. (1998). "High Performance Microprocessor Design". IEEE Journal of Solid-State Circuits, Volume 33, Number 5, pp. 676–686.

- Gwennap, Linley (28 October 1996). "Digital 21264 Sets New Standard". Microprocessor Report, Volume 10, Number 14. MicroDesign Resources.

- Kessler, R. E.; McLellan, E. J. and Webb, D. A. (1998) "The Alpha 21264 Microprocessor Architecture". Proceedings of the International Conference on Computer Design: VLSI in Computers and Processors. pp. 90–95.

- Kessler, R. E. (1999). "The Alpha 21264 Microprocessor". IEEE Micro, March–April 1999. pp. 24–36.

- Leibholz, Daniel and Razdan, Rahul (1997). "The Alpha 21264: A 500 MHz Out-of-Order Execution Microprocessor". Proceedings of Compcon '97. pp. 28–36.

- Matson, M. et al. "Circuit Implementation of a 600MHz Superscalar RISC Microprocessor". Proceedings of the International Conference on Computer Design: VLSI in Computers and Processors. pp. 104–110.

अग्रिम पठन

- Benschneider, B.J. et al. (2000). "A 1 GHz Alpha microprocessor". ISSCC Digest of Technical Papers, pp. 86–87.

- Clouser, J. et al. (July 1999). "A 600-MHz superscalar floating-point processor". IEEE Journal of Solid-State Circuits 34 (7): pp. 1026–1029.

- Fischer, T.; Leibholz, D. (1998). "Design trade offs in stall-control circuits for 600 MHz instruction queues". ISSCC Digest of Technical Papers, pp. 232–234, 444.

- Gieseke, B.A. et al. (1997). "A 600 MHz superscalar RISC microprocessor with out-of-order execution". ISSCC Digest of Technical Papers, pp. 176–177, 451.

- Gronowski, Paul E. et al. (May 1998). "High-performance microprocessor design". IEEE Journal of Solid-State Circuits 33 (5): pp. 676–686.

- Hokinson, R. et al. (2001). "Design and migration challenges for an Alpha microprocessor in a 0.18 μm copper process". ISSCC Digest of Technical Papers, pp. 320–321, 460.

- Templates that generate short descriptions

- Collapse templates

- Navigational boxes

- Navigational boxes without horizontal lists

- Sidebars with styles needing conversion

- Templates generating microformats

- Templates that are not mobile friendly

- Wikipedia metatemplates

- डीईसी माइक्रोप्रोसेसर

- सुपरस्केलर माइक्रोप्रोसेसर

- 64-बिट माइक्रोप्रोसेसर

- Machine Translated Page

- Created On 12/04/2024