एक चिप पर नेटवर्क

| a series का हिस्सा चालू | ||||

| नेटवर्क विज्ञान | ||||

|---|---|---|---|---|

| नेटवर्क प्रकार | ||||

| ग्राफ | ||||

|

||||

| मॉडल | ||||

|

||||

| ||||

चिप या नेटवर्क-ऑन-चिप पर एक नेटवर्क (NoC /ˌɛnˌoʊˈsiː/ en-oh-SEE या /nɒk/ knock)[nb 1] एक एकीकृत सर्किट (माइक्रोचिप) पर एक नेटवर्क सिद्धांत-आधारित [[संचार प्रणाली]] है, जो आमतौर पर एक चिप पर सिस्टम #फंक्शनल कंपोनेंट्स ऑन ए चिप (सिस्टम ऑन ए चिप) के बीच होती है। आईसी पर मॉड्यूल आमतौर पर सेमीकंडक्टर आईपी कोर होते हैं जो कंप्यूटर प्रणाली के विभिन्न कार्यों को योजनाबद्ध करते हैं, और नेटवर्क विज्ञान के अर्थ में प्रतिरूपकता (नेटवर्क) होने के लिए डिज़ाइन किए जाते हैं। चिप पर नेटवर्क SoC मॉड्यूलरिटी के बीच राउटर (कंप्यूटिंग) आधारित पैकेट बदली नेटवर्क है।

एनओसी तकनीक ऑन-चिप संचार के लिए संगणक संजाल के सिद्धांत और तरीकों को लागू करती है और पारंपरिक बस (कंप्यूटिंग) और क्रॉसबार स्विच नेटवर्क आर्किटेक्चर पर उल्लेखनीय सुधार लाती है। नेटवर्क-ऑन-चिप कई नेटवर्क टोपोलॉजी में आते हैं, जिनमें से कई अभी भी 2018 तक प्रायोगिक हैं।[citation needed]

2000 के दशक में शोधकर्ताओं ने पैकेट स्विचिंग नेटवर्क के रूप में एक प्रकार के ऑन-चिप इंटरकनेक्शन का प्रस्ताव देना शुरू किया था।[1] बस (कंप्यूटिंग) आधारित डिजाइन की मापनीयता के मुद्दों को संबोधित करने के लिए। पूर्ववर्ती शोधों ने उस डिजाइन का प्रस्ताव किया जो तारों को रूट करने के बजाय डेटा पैकेटों को रूट करता है।[2] फिर, चिप्स पर नेटवर्क की अवधारणा को 2002 में प्रस्तावित किया गया था।[3] एनओसी अन्य संचार सबसिस्टम डिजाइनों की तुलना में सिस्टम-ऑन-चिप की मापनीयता और जटिल एसओसी की शक्ति दक्षता में सुधार करते हैं। वे एक उभरती हुई प्रौद्योगिकियां हैं, निकट भविष्य में बड़े विकास के अनुमानों के साथ मल्टीकोर कंप्यूटर आर्किटेक्चर अधिक सामान्य हो गए हैं।

संरचना

This section needs expansion. You can help by adding to it. (October 2018) |

एनओसी सिंक्रोनस और एसिंक्रोनस क्लॉक डोमेन को [[ घड़ी डोमेन क्रॉसिंग ]] के रूप में जाना जाता है, या अनक्लॉक्ड अतुल्यकालिक सर्किट लॉजिक का उपयोग कर सकता है। एनओसी विश्व स्तर पर एसिंक्रोनस स्थानीय रूप से सिंक्रोनस का समर्थन करते हैं। वैश्विक रूप से एसिंक्रोनस, स्थानीय रूप से सिंक्रोनस इलेक्ट्रॉनिक्स आर्किटेक्चर, सिस्टम-ऑन-चिप पर प्रत्येक प्रोसेसर कोर या कार्यात्मक इकाई को अपना स्वयं का क्लॉक डोमेन रखने की अनुमति देता है।[4]

आर्किटेक्चर

This section needs expansion. You can help by adding to it. (October 2018) |

NoC आर्किटेक्चर आमतौर पर इंटरकनेक्शन तारों और पॉइंट-टू-पॉइंट (दूरसंचार) की संख्या, लंबाई, क्षेत्र और बिजली की खपत को सीमित करने के लिए विरलता छोटी दुनिया का नेटवर्क (SWNs) और स्केल-फ्री नेटवर्क (SFNs) को मॉडल करते हैं। .

टोपोलॉजी

टोपोलॉजी एनओसी डिज़ाइन का पहला मूलभूत पहलू है, और इसका समग्र नेटवर्क लागत और प्रदर्शन पर गहरा प्रभाव पड़ता है। टोपोलॉजी नोड्स और चैनलों के बीच भौतिक लेआउट और कनेक्शन निर्धारित करती है। इसके अलावा, संदेश ट्रैवर्स हॉप्स और प्रत्येक हॉप के चैनल की लंबाई टोपोलॉजी पर निर्भर करती है। इस प्रकार, टोपोलॉजी विलंबता और बिजली की खपत को महत्वपूर्ण रूप से प्रभावित करती है। इसके अलावा, चूंकि टोपोलॉजी नोड्स के बीच वैकल्पिक रास्तों की संख्या निर्धारित करती है, यह नेटवर्क ट्रैफ़िक वितरण को प्रभावित करती है, और इसलिए नेटवर्क बैंडविड्थ और प्रदर्शन प्राप्त होता है।

लाभ

परंपरागत रूप से, IC को समर्पित पॉइंट-टू-पॉइंट (दूरसंचार) | पॉइंट-टू-पॉइंट कनेक्शन के साथ डिज़ाइन किया गया है, जिसमें प्रत्येक सिग्नल के लिए एक तार समर्पित होता है। इसका परिणाम घना नेटवर्क में होता है। बड़े डिज़ाइनों के लिए, विशेष रूप से, इसमें एकीकृत सर्किट डिज़ाइन के दृष्टिकोण से कई सीमाएँ हैं। इसके लिए इंटरकनेक्शन की संख्या में बिजली की खपत द्विघात फ़ंक्शन की आवश्यकता होती है। तार डाई (एकीकृत सर्किट) के अधिकांश हिस्से पर कब्जा कर लेते हैं, और नैनोमीटर सीएमओएस तकनीक में, इंटरकनेक्ट प्रदर्शन और गतिशील शक्ति अपव्यय दोनों पर हावी हो जाते हैं, क्योंकि चिप में तारों में सिग्नल प्रसार के लिए कई घड़ी चक्रों की आवश्यकता होती है। यह अधिक परजीवी समाई, परजीवी तत्व (विद्युत नेटवर्क) को सर्किट पर जमा करने की अनुमति देता है। (प्वाइंट-टू-पॉइंट कनेक्शन के लिए वायरिंग आवश्यकताओं की चर्चा के लिए रेंट का नियम देखें)।

संचार सबसिस्टम में विरल नेटवर्क और इंटरकनेक्शन के संदर्भ की लोकैलिटी पारंपरिक बस (कंप्यूटिंग)-आधारित और क्रॉसबार स्विच-आधारित सिस्टम पर कई सुधार देती है।

समानता और मापनीयता

नेटवर्क-ऑन-चिप के लिंक में तार कई सिग्नलिंग (दूरसंचार) द्वारा साझा किए जाते हैं। समानांतर कंप्यूटिंग का एक उच्च स्तर हासिल किया जाता है, क्योंकि एनओसी में सभी डेटा लिंक अलग-अलग पैकेट स्विचिंग पर एक साथ काम कर सकते हैं।[why?] इसलिए, जैसे-जैसे बहुत बड़े पैमाने पर एकीकरण की जटिलता बढ़ती रहती है, एक एनओसी पिछले संचार आर्किटेक्चर (जैसे, समर्पित पॉइंट-टू-पॉइंट सिग्नल तार , साझा बस (कंप्यूटिंग) की तुलना में बेहतर प्रदर्शन (जैसे THROUGHPUT) और स्केलेबिलिटी प्रदान करता है। ), या खंडित बसें नेटवर्क ब्रिज के साथ)। कलन विधि[which?] को इस तरह से डिज़ाइन किया जाना चाहिए कि वे बड़े पैमाने पर समानांतर प्रदान करते हैं और इसलिए एनओसी की क्षमता का उपयोग कर सकते हैं।

वर्तमान शोध

कुछ शोधकर्ता[who?] सोचते हैं कि एनओसी को सेवा की गुणवत्ता (क्यूओएस) का समर्थन करने की आवश्यकता है, अर्थात् थ्रूपुट, एंड-टू-एंड देरी, निष्पक्षता उपाय के संदर्भ में विभिन्न आवश्यकताओं को प्राप्त करें,[5] और समय सीमा।[citation needed] ऑडियो और वीडियो प्लेबैक सहित रीयल-टाइम संगणना, QoS समर्थन प्रदान करने का एक कारण है। हालांकि, VxWorks, RTLinux या QNX जैसे मौजूदा सिस्टम कार्यान्वयन विशेष हार्डवेयर के बिना उप-मिलीसेकंड रीयल-टाइम कंप्यूटिंग प्राप्त करने में सक्षम हैं।[citation needed]

यह संकेत दे सकता है कि कई रीयल-टाइम कंप्यूटिंग | रीयल-टाइम अनुप्रयोगों के लिए मौजूदा ऑन-चिप इंटरकनेक्ट इंफ्रास्ट्रक्चर की सेवा गुणवत्ता पर्याप्त है, और समर्पित हार्डवेयर तर्क माइक्रोसेकेंड परिशुद्धता प्राप्त करने के लिए आवश्यक होगा, एक डिग्री जो अंत के लिए अभ्यास में शायद ही कभी जरूरी है उपयोगकर्ता (ध्वनि या वीडियो जिटर को मिलीसेकंड विलंबता गारंटी के केवल दसवें हिस्से की आवश्यकता होती है)। सेवा की एनओसी-स्तर की गुणवत्ता (क्यूओएस) के लिए एक और प्रेरणा एक सार्वजनिक क्लाउड कम्प्यूटिंग इंफ्रास्ट्रक्चर में एकल मल्टी-कोर (कंप्यूटिंग) के संसाधनों को साझा करने वाले एकाधिक समवर्ती उपयोगकर्ताओं का समर्थन करना है। ऐसे मामलों में, हार्डवेयर QoS लॉजिक सेवा प्रदाता को सेवा के उस स्तर पर सेवा-स्तर का समझौता करने में सक्षम बनाता है जो एक उपयोगकर्ता को प्राप्त होता है, एक ऐसी सुविधा जिसे कुछ कॉर्पोरेट या सरकारी ग्राहकों द्वारा वांछनीय समझा जा सकता है।[citation needed]

भौतिक लिंक स्तर से लेकर नेटवर्क स्तर तक और सिस्टम आर्किटेक्चर और एप्लिकेशन सॉफ़्टवेयर तक सभी स्तरों पर कई चुनौतीपूर्ण शोध समस्याओं का समाधान किया जाना बाकी है। चिप पर नेटवर्क पर पहली समर्पित शोध संगोष्ठी मई 2007 में प्रिंसटन विश्वविद्यालय में आयोजित की गई थी।[6] नेटवर्क-ऑन-चिप पर इलेक्ट्रिकल और इलेक्ट्रॉनिक्स इंजीनियर्स अंतर्राष्ट्रीय संगोष्ठी का दूसरा संस्थान अप्रैल 2008 में न्यूकैसल विश्वविद्यालय में आयोजित किया गया था।

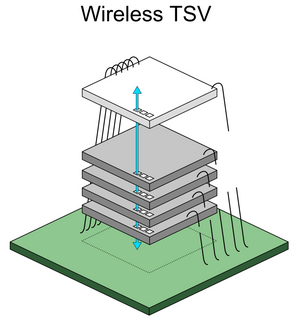

इंटीग्रेटेड वेवगाइड (ऑप्टिक्स) और एक चिप (ओएनओसी) पर ऑप्टिकल नेटवर्क वाले उपकरणों पर शोध किया गया है।[7][8] एनओसी के प्रदर्शन को बढ़ाने का संभावित तरीका चिप्सलेट के बीच वायरलेस संचार चैनलों का उपयोग है - चिप पर वायरलेस नेटवर्क (वाईएनओसी) नामित।[9]

== एनओसी == के साइड बेनिफिट्स

एनओसी से जुड़े मल्टी-कोर सिस्टम में, सुसंगतता संदेशों और कैश मिस अनुरोधों को स्विच पास करना पड़ता है। तदनुसार, सरल ट्रैकिंग और अग्रेषण तत्वों के साथ स्विच को बढ़ाया जा सकता है ताकि यह पता लगाया जा सके कि भविष्य में कौन से कैश ब्लॉक को कोर द्वारा अनुरोध किया जाएगा। फिर, अग्रेषण तत्व किसी भी अनुरोधित ब्लॉक को सभी कोर में मल्टीकास्ट करते हैं जो भविष्य में ब्लॉक का अनुरोध कर सकते हैं। यह तंत्र कैश मिस रेट को कम करता है। <रेफरी नाम = साझा कैश मिस को कम करने के लिए ट्री-आधारित योजना

दर उत्तोलन क्षेत्रीय, सांख्यिकीय और लौकिक

समानताएं >Marzieh Lenjani, Mahmoud Reza Hashemi (2014). "क्षेत्रीय, सांख्यिकीय और लौकिक समानताओं का लाभ उठाते हुए साझा कैश मिस रेट को कम करने के लिए ट्री-आधारित योजना". IET Computers & Digital Techniques. 8: 30–48. doi:10.1049/iet-cdt.2011.0066.{{cite journal}}: CS1 maint: uses authors parameter (link)</ref>

बेंचमार्क

एनओसी विकास और अध्ययन के लिए विभिन्न प्रस्तावों और विकल्पों की तुलना करने की आवश्यकता होती है। इस तरह के मूल्यांकन में मदद करने के लिए एनओसी ट्रैफिक पैटर्न का विकास किया जा रहा है। मौजूदा एनओसी बेंचमार्क में एनओसीबेंच और एमसीएसएल एनओसी ट्रैफिक पैटर्न शामिल हैं।[10]

इंटरकनेक्ट प्रोसेसिंग यूनिट

इंटरकनेक्ट प्रोसेसिंग यूनिट (IPU)[11] कंप्यूटर हार्डवेयर और सॉफ़्टवेयर घटकों के साथ एक ऑन-चिप संचार नेटवर्क है जो एक चिप पर विभिन्न सिस्टम के प्रमुख कार्यों को संयुक्त रूप से लागू करता है। सिस्टम-ऑन-चिप प्रोग्रामिंग मॉडल संचार और तुल्यकालन आदिम के एक सेट के माध्यम से और उच्च और निम्न-स्तर प्रदान करता है। निम्न उन्नत सुविधाओं को सक्षम करने के लिए -लेवल प्लेटफॉर्म सेवाएं[which?] आधुनिक विषम अनुप्रयोगों में[definition needed] सिंगल डाई (इंटीग्रेटेड सर्किट) पर।

यह भी देखें

- धमनी

- इलेक्ट्रॉनिक डिजाइन स्वचालन (EDA)

- एकीकृत सर्किट डिजाइन

- कुडा

- वैश्विक रूप से अतुल्यकालिक स्थानीय रूप से तुल्यकालिक | विश्व स्तर पर अतुल्यकालिक, स्थानीय रूप से तुल्यकालिक

- नेटवर्क आर्किटेक्चर

टिप्पणियाँ

- ↑ This article uses the convention that "NoC" is pronounced /nɒk/ nock. Therefore, it uses the convention "a" for the indefinite article corresponding to NoC ("a NoC"). Other sources may pronounce it as /ˌɛnˌoʊˈsiː/ en-oh-SEE and therefore use "an NoC".

संदर्भ

- ↑ Guerrier, P.; Greiner, A. (2000). "ऑन-चिप पैकेट-स्विच्ड इंटरकनेक्शन के लिए एक सामान्य संरचना". Proceedings Design, Automation and Test in Europe Conference and Exhibition 2000 (Cat. No. PR00537). Paris, France: IEEE Comput. Soc: 250–256. doi:10.1109/DATE.2000.840047. ISBN 978-0-7695-0537-4. Archived from the original on 2022-10-22. Retrieved 2022-11-23.

- ↑ Proceedings, 2001 Design Automation Conference : 38th DAC : Las Vegas Convention Center, Las Vegas, NV, June 18-22, 2001. Association for Computing Machinery, ACM Special Interest Group on Design Automation. New York, N.Y.: Association for Computing Machinery. 2001. ISBN 1-58113-297-2. OCLC 326240184.

{{cite book}}: CS1 maint: others (link) - ↑ Benini, L.; De Micheli, G. (January 2002). "Networks on chips: a new SoC paradigm". Computer. 35 (1): 70–78. doi:10.1109/2.976921. Archived from the original on 2022-10-22. Retrieved 2022-11-23.

- ↑ Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-chip: the Next Generation of System-on-Chip Integration (1st ed.). Boca Raton, FL: CRC Press. p. 3. ISBN 9781466565272. OCLC 895661009.

- ↑ "चिप-मल्टीप्रोसेसरों के लिए मल्टी-एप्लीकेशन मैपिंग में ऑन-चिप नेटवर्क लेटेंसी को संतुलित करना". IPDPS. May 2014.

- ↑ NoCS 2007 Archived 2008-09-01 at the Wayback Machine website.

- ↑ On-Chip Networks Bibliography[permanent dead link]

- ↑ "Inter/Intra-Chip Optical Network Bibliography-". Archived from the original on 2015-09-23. Retrieved 2015-07-02.

- ↑ Slyusar V. I., Slyusar D.V. Pyramidal design of nanoantennas array. // VIII International Conference on Antenna Theory and Techniques (ICATT’11). - Kyiv, Ukraine. - National Technical University of Ukraine “Kyiv Polytechnic Institute”. - September 20–23, 2011. - Pp. 140 - 142. [1] Archived 2019-07-17 at the Wayback Machine

- ↑ "एनओसी ट्रैफिक". www.ece.ust.hk. Archived from the original on 2017-12-25. Retrieved 2018-10-08.

- ↑ Marcello Coppola, Miltos D. Grammatikakis, Riccardo Locatelli, Giuseppe Maruccia, Lorenzo Pieralisi, "Design of Cost-Efficient Interconnect Processing Units: Spidergon STNoC", CRC Press, 2008, ISBN 978-1-4200-4471-3

Adapted from Avinoam Kolodny's's column in the ACM SIGDA e-newsletter by Igor Markov

The original text can be found at http://www.sigda.org/newsletter/2006/060415.txt

अग्रिम पठन

- Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-chip: the Next Generation of System-on-Chip Integration (1st ed.). Boca Raton, FL: CRC Press. ISBN 9781466565272. OCLC 895661009.

- Sheng Ma, Libo Huang, Mingche Lai, Wei Shi, Zhiying Wang (2014). Networks-on-Chip: From Implementations to Programming Paradigms (1st ed.). Amsterdam, NL: Morgan Kaufmann. ISBN 9780128011782. OCLC 894609116.

{{cite book}}: CS1 maint: uses authors parameter (link) - Giorgios Dimitrakopoulos, Anastasios Psarras, Ioannis Seitanidis (2014-08-27). Microarchitecture of Network-on-Chip Routers: A Designer's Perspective (1st ed.). New York, NY. ISBN 9781461443018. OCLC 890132032.

{{cite book}}: CS1 maint: uses authors parameter (link) - Natalie Enright Jerger, Tushar Krishna, Li-Shiuan Peh (2017-06-19). On-chip Networks (2nd ed.). San Rafael, California. ISBN 9781627059961. OCLC 991871622.

{{cite book}}: CS1 maint: uses authors parameter (link) - Marzieh Lenjani, Mahmoud Reza Hashemi (2014). "Tree-based scheme for reducing shared cache miss rate leveraging regional, statistical and temporal similarities". IET Computers & Digital Techniques. 8: 30–48. doi:10.1049/iet-cdt.2011.0066.

{{cite journal}}: CS1 maint: uses authors parameter (link)

बाहरी संबंध

- DATE 2006 workshop on NoC

- NoCS 2007 - The 1st ACM/IEEE International Symposium on Networks-on-Chip

- NoCS 2008 - The 2nd IEEE International Symposium on Networks-on-Chip

- Jean-Jacques Lecler, Gilles Baillieu, Design Automation for Embedded Systems (Springer), "Application driven network-on-chip architecture exploration & refinement for a complex SoC", June 2011, Volume 15, Issue 2, pp 133–158, doi:10.1007/s10617-011-9075-5 [Online] http://www.arteris.com/hs-fs/hub/48858/file-14363521-pdf/docs/springer-appdrivennocarchitecture8.5x11.pdf

- CS1 maint: others

- Articles with dead external links from February 2023

- Templates that generate short descriptions

- Use American English from October 2018

- Articles with unsourced statements from August 2022

- Articles using small message boxes

- Wikipedia articles needing clarification from October 2018

- All articles with specifically marked weasel-worded phrases

- Articles with specifically marked weasel-worded phrases from October 2018

- Articles with specifically marked weasel-worded phrases from June 2015

- Articles with unsourced statements from June 2015

- Collapse templates

- Navigational boxes

- Navigational boxes without horizontal lists

- Sidebars with styles needing conversion

- Templates generating microformats

- Templates that are not mobile friendly

- Wikipedia metatemplates

- चिप पर नेटवर्क

- इलेक्ट्रॉनिक डिजाइन स्वचालन

- एकीकृत सर्किट

- एक चिप पर सिस्टम

- हार्डवेयर एक्सिलरेशन

- नेटवर्क सिद्धांत

- कम्प्यूटर नेट्वर्किंग

- समानांतर कंप्यूटिंग

- संचार सर्किट

- प्रतिरूपकता

- Machine Translated Page

- Created On 27/04/2023