फ़्लोटिंग-पॉइंट इकाई

एक फ़्लोटिंग-पॉइंट यूनिट (एफपीयू, बोलचाल की भाषा में एक गणित सहप्रोसेसर) एक कंप्यूटर सिस्टम का एक हिस्सा है जिसे विशेष रूप से फ़्लोटिंग-पॉइंट अंकगणित | फ़्लोटिंग-पॉइंट संख्याओं पर संचालन करने के लिए डिज़ाइन किया गया है।[1] विशिष्ट संक्रियाएँ जोड़, घटाव, गुणा, भाग (गणित), और वर्गमूल हैं। कुछ एफपीयू विभिन्न पारलौकिक कार्य भी कर सकते हैं जैसे घातांक प्रकार्य या त्रिकोणमितीय गणना, लेकिन सटीकता बहुत कम हो सकती है,[2][3] ताकि कुछ सिस्टम सॉफ़्टवेयर में इन कार्यों की गणना करना पसंद करें।

सामान्य प्रयोजन के कंप्यूटर आर्किटेक्चर में, एक या अधिक एफपीयू को केंद्रीय प्रसंस्करण इकाई के भीतर निष्पादन इकाइयों के रूप में एकीकृत किया जा सकता है; हालाँकि, कई एंबेडेड प्रोसेसर में फ़्लोटिंग-पॉइंट ऑपरेशन के लिए हार्डवेयर समर्थन नहीं होता है (जबकि वे तेजी से उन्हें मानक के रूप में रखते हैं, कम से कम 32-बिट वाले)।

जब एक सीपीयू एक प्रोग्राम निष्पादित कर रहा है जो फ्लोटिंग-पॉइंट ऑपरेशन के लिए कहता है, तो इसे पूरा करने के तीन तरीके हैं:

- एक फ़्लोटिंग-पॉइंट यूनिट एमुलेटर (एक फ़्लोटिंग-पॉइंट लाइब्रेरी)

- ऐड-ऑन एफपीयू

- एकीकृत एफपीयू

इतिहास

1954 में, IBM 704 में एक मानक सुविधा के रूप में फ़्लोटिंग-पॉइंट अंकगणित था, जो इसके पूर्ववर्ती IBM 701 की तुलना में इसके प्रमुख सुधारों में से एक था। इसे इसके उत्तराधिकारियों 709, 7090 और 7094 में आगे बढ़ाया गया था।

1963 में, डिजिटल ने पीडीपी-6 की घोषणा की, जिसमें एक मानक सुविधा के रूप में फ्लोटिंग पॉइंट था।[4] 1963 में, GE-200 श्रृंखला|GE-235 में फ्लोटिंग पॉइंट और डबल-प्रिसिजन गणनाओं के लिए एक सहायक अंकगणितीय इकाई शामिल थी।[5] ऐतिहासिक रूप से, कुछ प्रणालियों ने फ़्लोटिंग-पॉइंट अंकगणित को एक एकीकृत इकाई के बजाय एक सह प्रोसेसर के साथ लागू किया (लेकिन अब सीपीयू के अलावा, उदाहरण के लिए ग्राफ़िक्स प्रोसेसिंग युनिट ) – जो सहसंसाधक होते हैं जो हमेशा सीपीयू में निर्मित नहीं होते हैं – एक नियम के रूप में एफपीयू है, जबकि जीपीयू की पहली पीढ़ी नहीं थी)। यह एक एकल एकीकृत सर्किट, एक संपूर्ण मुद्रित सर्किट बोर्ड या एक कैबिनेट हो सकता है। जहां फ़्लोटिंग-पॉइंट गणना हार्डवेयर प्रदान नहीं किया गया है, फ़्लोटिंग-पॉइंट गणना सॉफ़्टवेयर में की जाती है, जिसमें अधिक प्रोसेसर समय लगता है, लेकिन अतिरिक्त हार्डवेयर की लागत से बचा जाता है। किसी विशेष कंप्यूटर आर्किटेक्चर के लिए, फ़्लोटिंग-पॉइंट यूनिट निर्देश सॉफ़्टवेयर फ़ंक्शंस की लाइब्रेरी द्वारा एम्यूलेटर हो सकते हैं; यह समान वस्तु कोड को फ़्लोटिंग-पॉइंट हार्डवेयर के साथ या उसके बिना सिस्टम पर चलने की अनुमति दे सकता है। अनुकरण को कई स्तरों पर लागू किया जा सकता है: सीपीयू में माइक्रोकोड के रूप में (सामान्य अभ्यास नहीं), एक ऑपरेटिंग सिस्टम फ़ंक्शन के रूप में, या उपयोगकर्ता-स्पेस कोड में। जब केवल पूर्णांक कार्यक्षमता उपलब्ध होती है, तो CORDIC फ़्लोटिंग-पॉइंट इम्यूलेशन विधियों का सबसे अधिक उपयोग किया जाता है।

अधिकांश आधुनिक कंप्यूटर आर्किटेक्चर में, पूर्णांक संचालन से फ़्लोटिंग-पॉइंट संचालन का कुछ विभाजन होता है। यह विभाजन वास्तुकला के अनुसार काफी भिन्न होता है; कुछ के पास समर्पित फ़्लोटिंग-पॉइंट रजिस्टर हैं, जबकि कुछ, x86 की तरह, इसे स्वतंत्र कंप्यूटर घड़ी योजनाओं के रूप में लेते हैं।[6] CORDIC रूटीन को x87 कोप्रोसेसर (इंटेल 8087) में लागू किया गया है[7][8][9][10][11] 80287,[11][12] 80387[11][12] इंटेल 80486 तक[7]माइक्रोप्रोसेसर श्रृंखला, साथ ही मोटोरोला 68881 में भी[7][8]और 68882 कुछ प्रकार के फ़्लोटिंग-पॉइंट निर्देशों के लिए, मुख्य रूप से एफपीयू सबसिस्टम के तर्क द्वार काउंट (और जटिलता) को कम करने के तरीके के रूप में।

फ़्लोटिंग-पॉइंट ऑपरेशन अक्सर निर्देश पाइपलाइनिंग होते हैं। सामान्य आउट-ऑफ़-ऑर्डर निष्पादन के बिना पहले के सुपरस्केलर आर्किटेक्चर में, फ़्लोटिंग-पॉइंट ऑपरेशंस को कभी-कभी पूर्णांक ऑपरेशंस से अलग से पाइपलाइन किया जाता था।

बुलडोजर (माइक्रोआर्किटेक्चर) का मॉड्यूलर आर्किटेक्चर फ्लेक्सएफपीयू नामक एक विशेष एफपीयू का उपयोग करता है, जो एक साथ मल्टीथ्रेडिंग का उपयोग करता है। प्रत्येक भौतिक पूर्णांक कोर, प्रति मॉड्यूल दो, एकल-थ्रेडेड है, इंटेल के हाइपर थ्रेडिंग के विपरीत, जहां दो आभासी एक साथ थ्रेड एक ही भौतिक कोर के संसाधनों को साझा करते हैं।[13][14]

फ़्लोटिंग-पॉइंट लाइब्रेरी

कुछ फ़्लोटिंग-पॉइंट हार्डवेयर केवल सबसे सरल ऑपरेशन का समर्थन करते हैं: जोड़, घटाव और गुणा। लेकिन यहां तक कि सबसे जटिल फ़्लोटिंग-पॉइंट हार्डवेयर में भी सीमित संख्या में संचालन होते हैं जो इसे समर्थन दे सकते हैं – उदाहरण के लिए, कोई भी एफपीयू सीधे तौर पर मनमाना-सटीक अंकगणित का समर्थन नहीं करता है।

जब एक सीपीयू एक प्रोग्राम निष्पादित कर रहा है जो एक फ़्लोटिंग-पॉइंट ऑपरेशन की मांग करता है जो सीधे हार्डवेयर द्वारा समर्थित नहीं है, तो सीपीयू सरल फ़्लोटिंग-पॉइंट ऑपरेशंस की एक श्रृंखला का उपयोग करता है। बिना किसी फ्लोटिंग-पॉइंट हार्डवेयर वाले सिस्टम में, सीपीयू एमुलेटर सरल फिक्स्ड-पॉइंट अंकगणितीय संचालन की एक श्रृंखला का उपयोग करता है जो पूर्णांक अंकगणितीय तर्क इकाई पर चलता है।

वह सॉफ़्टवेयर जो फ़्लोटिंग-पॉइंट ऑपरेशंस का अनुकरण करने के लिए संचालन की आवश्यक श्रृंखला को सूचीबद्ध करता है, अक्सर फ़्लोटिंग-पॉइंट पुस्तकालय (कंप्यूटिंग) में पैक किया जाता है।

एकीकृत एफपीयू

कुछ मामलों में, एफपीयू को विशिष्ट किया जा सकता है, और सरल फ़्लोटिंग-पॉइंट ऑपरेशंस (मुख्य रूप से जोड़ और गुणा) और विभाजन जैसे अधिक जटिल ऑपरेशंस के बीच विभाजित किया जा सकता है। कुछ मामलों में, केवल सरल ऑपरेशन को हार्डवेयर या माइक्रोकोड में लागू किया जा सकता है, जबकि अधिक जटिल ऑपरेशन को सॉफ्टवेयर के रूप में लागू किया जाता है।

कुछ मौजूदा आर्किटेक्चर में, SIMD गणना करने के लिए FPU कार्यक्षमता को एकल निर्देश, एकाधिक डेटा इकाइयों के साथ जोड़ा जाता है; इसका एक उदाहरण नए इंटेल और एएमडी प्रोसेसर में उपयोग किए गए x86-64 आर्किटेक्चर में स्ट्रीमिंग SIMD एक्सटेंशन निर्देश सेट के साथ x87 निर्देशों का संवर्द्धन है।

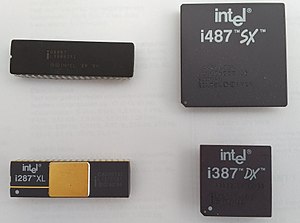

ऐड-ऑन एफपीयू

पीडीपी-11 के कई मॉडल, जैसे पीडीपी-11/45,[15] पीडीपी-11/34ए,[16]: 184–185 पीडीपी-11/44,[16]: 195, 211 और पीडीपी-11/70,[16]: 277, 286–287 फ़्लोटिंग-पॉइंट निर्देशों का समर्थन करने के लिए एक ऐड-ऑन फ़्लोटिंग-पॉइंट इकाई का समर्थन करता है। पीडीपी-11/60,[16]: 261 माइक्रोपीडीपी-11/23[17] और कई VAX मॉडल[18][19] ऐड-ऑन एफपीयू के बिना फ्लोटिंग-पॉइंट निर्देशों को निष्पादित कर सकता है (माइक्रोपीडीपी-11/23 को इसके लिए ऐड-ऑन माइक्रोकोड विकल्प की आवश्यकता होती है)[17]), और उन निर्देशों के निष्पादन में तेजी लाने के लिए ऐड-ऑन एक्सेलेरेटर की पेशकश की।

1980 के दशक में, आईबीएम पीसी/संगत माइक्रो कंप्यूटरों में एफपीयू का सेंट्रल प्रोसेसिंग यूनिट से पूरी तरह अलग होना आम बात थी, और आमतौर पर इसे वैकल्पिक ऐड-ऑन के रूप में बेचा जाता था। इसे केवल तभी खरीदा जाएगा जब गणित-गहन कार्यक्रमों को तेज़ करने या सक्षम करने के लिए आवश्यक हो।

आईबीएम पीसी, आईबीएम पर्सनल कंप्यूटर एक्सटी, और 8088 या 8086 पर आधारित अधिकांश कंपैटिबल में वैकल्पिक 8087 कोप्रोसेसर के लिए एक सॉकेट था। आईबीएम पर्सनल कंप्यूटर/एटी और इंटेल 80286-आधारित सिस्टम आमतौर पर x87#80287 और इंटेल 80386|80386/80386SX-आधारित मशीनों के लिए सॉकेट किए गए थे। – क्रमशः x87#80387 और Intel 80387SX के लिए, हालाँकि शुरुआती वाले 80287 के लिए सॉकेट किए गए थे, क्योंकि 80387 अभी तक अस्तित्व में नहीं था। अन्य कंपनियों ने Intel x86 श्रृंखला के लिए सह-प्रोसेसर का निर्माण किया। इनमें साइरिक्स और दूर शामिल थे। बलूत का फल कंप्यूटर ने एकल-परिशुद्धता फ़्लोटिंग-पॉइंट प्रारूप , डबल-परिशुद्धता फ़्लोटिंग-पॉइंट प्रारूप और विस्तारित परिशुद्धता की पेशकश के लिए WE32206 को चुना।[20] इसकी एआरएम वास्तुकला संचालित बलूत का फल आर्किमिडीज़ रेंज के लिए।

मोटोरोला 68000 श्रृंखला, मोटोरोला 68881 के लिए सहप्रोसेसर उपलब्ध थे। ये सन-3 श्रृंखला की तरह मोटोरोला 68020/मोटोरोला 68030-आधारित कार्य केंद्र में आम थे। उन्हें आम तौर पर ऐप्पल मैकिनटोश और कमोडोर अमिगा श्रृंखला के उच्च-अंत मॉडल में भी जोड़ा गया था, लेकिन आईबीएम पीसी-संगत सिस्टम के विपरीत, कोप्रोसेसर को जोड़ने के लिए सॉकेट निचले-अंत सिस्टम में उतने आम नहीं थे।

microcontroller इकाइयों (एमसीयू/μCs)/सिंगल-बोर्ड कंप्यूटर (एसबीसी) के लिए ऐड-ऑन एफपीयू कोप्रोसेसर इकाइयां भी हैं, जो फ्लोटिंग-पॉइंट अंकगणितीय क्षमता प्रदान करने का काम करती हैं। ये ऐड-ऑन एफपीयू होस्ट-प्रोसेसर-स्वतंत्र हैं, उनकी अपनी प्रोग्रामिंग आवश्यकताएं (गणितीय संचालन, निर्देश सेट इत्यादि) होती हैं और अक्सर अपने स्वयं के एकीकृत विकास वातावरण (आईडीई) के साथ प्रदान की जाती हैं।

यह भी देखें

- अंकगणितीय तर्क इकाई (एएलयू)

- पता निर्माण इकाई (एजीयू)

- लोड-स्टोर इकाई

- कॉर्डिक रूटीन का उपयोग कई एफपीयू में कार्यों को लागू करने के लिए किया जाता है लेकिन गेट गिनती में बहुत अधिक वृद्धि नहीं होती है

- निष्पादन इकाई

- IEEE 754 फ़्लोटिंग-पॉइंट मानक

- आईबीएम हेक्साडेसिमल फ़्लोटिंग पॉइंट

- ग्राफ़िक्स प्रोसेसिंग युनिट

- गुणा-संचय संचालन

संदर्भ

- ↑ Anderson, Stanley F.; Earle, John G.; Goldschmidt, Robert Elliott; Powers, Don M. (January 1967). "The IBM System/360 Model 91: Floating-Point Execution Unit". IBM Journal of Research and Development. 11 (1): 34–53. doi:10.1147/rd.111.0034. ISSN 0018-8646.

- ↑ Bruce Dawson (2014-10-09). "Intel Underestimates Error Bounds by 1.3 quintillion". randomascii.wordpress.com. Retrieved 2020-01-16.

- ↑ "FSIN Documentation Improvements in the "Intel® 64 and IA-32 Architectures Software Developer's Manual"". intel.com. 2014-10-09. Archived from the original on 2020-01-16. Retrieved 2020-01-16.

- ↑ "PDP-6 Handbook" (PDF). www.bitsavers.org. Archived (PDF) from the original on 2022-10-09.

- ↑ "GE-2xx documents". www.bitsavers.org. CPB-267_GE-235-SystemManual_1963.pdf, p. IV-4.

- ↑ "Intel 80287 family". www.cpu-world.com. Retrieved 2019-01-15.

- ↑ 7.0 7.1 7.2 Muller, Jean-Michel (2006). प्राथमिक कार्य: एल्गोरिदम और कार्यान्वयन (2 ed.). Boston: Birkhäuser. p. 134. ISBN 978-0-8176-4372-0. LCCN 2005048094. Retrieved 2015-12-01.

- ↑ Palmer, John F.; Morse, Stephen Paul (1984). 8087 प्राइमर (1 ed.). John Wiley & Sons Australia, Limited. ISBN 0471875694. 9780471875697. Retrieved 2016-01-02.

- ↑ Glass, L. Brent (January 1990). "गणित सहसंसाधक: वे क्या करते हैं और कैसे करते हैं, इस पर एक नज़र". Byte. 15 (1): 337–348. ISSN 0360-5280.

- ↑ 11.0 11.1 11.2 Jarvis, Pitts (1990-10-01). "कॉर्डिक एल्गोरिदम को लागू करना - पारलौकिक कार्यों की गणना के लिए एक एकल कॉम्पैक्ट रूटीन". Dr. Dobb's Journal: 152–156. Retrieved 2016-01-02.

- ↑ 12.0 12.1 Yuen, A. K. (1988). "इंटेल के फ्लोटिंग-प्वाइंट प्रोसेसर". Electro/88 Conference Record: 48/5/1–7.

- ↑ "संग्रहीत प्रति". cdn3.wccftech.com. Archived from the original on 9 May 2015. Retrieved 14 March 2022.

- ↑ "एएमडी ने फ्लेक्स एफपी का अनावरण किया". bit-tech.net. Retrieved 29 March 2018.

- ↑ PDP-11/45 Processor Handbook (PDF). Digital Equipment Corporation. 1973. Chapter 7 "Floating Point Processor".

- ↑ 16.0 16.1 16.2 16.3 पीडीपी-11 प्रोसेसर हैंडबुक (PDF). Digital Equipment Corporation. 1979.

- ↑ 17.0 17.1 MICRO/PDP-11 Handbook (PDF). Digital Equipment Corporation. 1983. p. 33.

- ↑ VAX- Hardware Handbook Volume I-1986 (PDF). Digital Equipment Corporation. 1985.

- ↑ VAX- Hardware Handbook Volume II-1986 (PDF). Digital Equipment Corporation. 1986.

- ↑ "Western Electric 32206 co-processor". www.cpu-world.com. Retrieved 2021-11-06.

अग्रिम पठन

- Filiatreault, Raymond (2003). "SIMPLY FPU".

- Templates that generate short descriptions

- Collapse templates

- Navigational boxes

- Navigational boxes without horizontal lists

- Sidebars with styles needing conversion

- Templates generating microformats

- Templates that are not mobile friendly

- Wikipedia metatemplates

- सेंट्रल प्रोसेसिंग यूनिट

- कंप्यूटर अंकगणित

- सहसंसाधक

- तैरनेवाला स्थल

- Machine Translated Page

- Created On 25/07/2023